■従来のFPGAを進化させたSoCに実装する

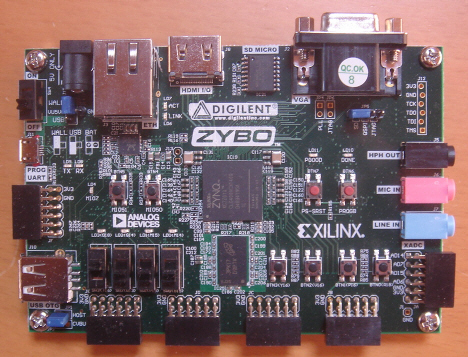

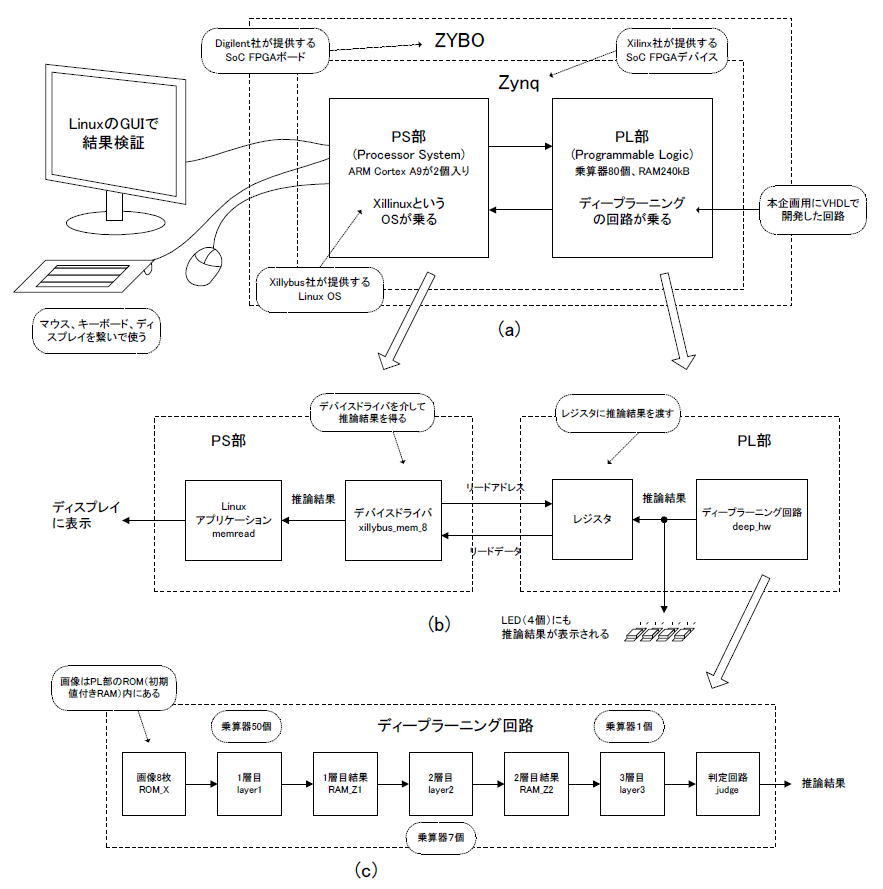

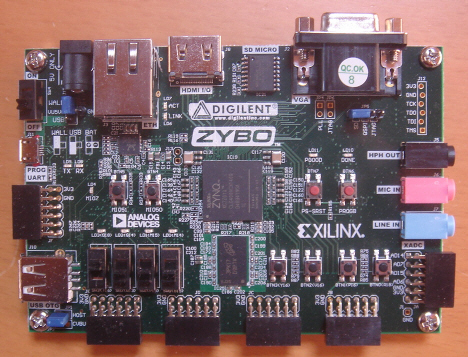

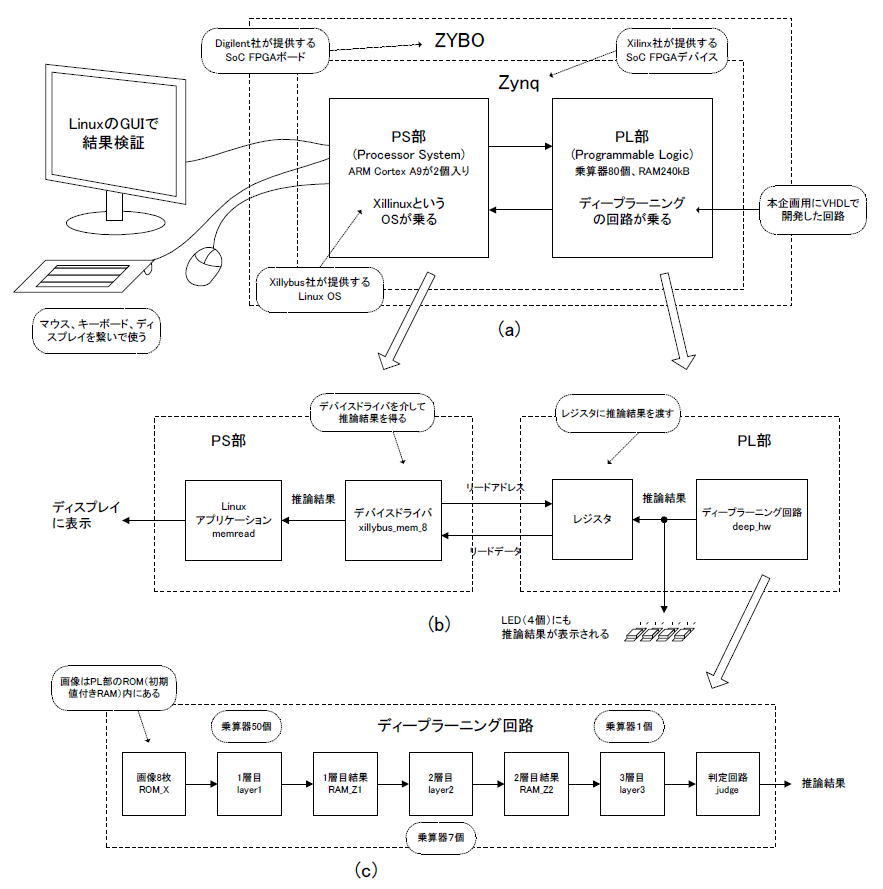

図4-01にその全体像を示します。ZYBOには「Zynq」というXilinx(ザイリンクス)社が提供するSoC FPGAデバイス(*1)が搭載されています。

(*1)従来のFPGAに加えてARM Cortex-A9という高速プロセッサを2個内蔵したデバイス。Linuxのような本格的なOSをのせ、マウス、キーボード、ディスプレイを繋いで使用することが多い。

●PS部に高速なARMプロセッサ

Zynqというデバイスは図4-01(a)のように「PS(Processor System)部」と「PL(Program Logic)部」に分かれています。

PS部にはARM Cortex-A9という高速プロセッサが2個あり、それぞれ650MHzで動作するので「Xillinux(ジーリナックス)」というXillybus(ジリーバス)社の提供するOSをのせ、ユーザーはマウス、キーボード、ディスプレイを繋いでパソコンのように操作します。

●PL部に多数のロジック、乗算器、RAM

PL部は従来のFPGAと同じようにLUT(Look Up Table、ロジックが一塊になったようなもの)が多数あり、ユーザーはそれらを自由に配線して使用できます。また、DSP(Digital Signal Processor、高速の乗算器などを含む回路)が80個、BRAM(Block RAM)が240kByteあり、それらも自由に使用できます。 |