4-03 ディープラーニング回路を含んだビットストリームの生成

この書籍の第3部・第1章、「ZYBOにLinuxをのせて使ってみる−OSからFPGAのロジックを制御」ではOSからLED点灯させたり、スイッチの値を読んだりします。この章を一通り試してから以下に進むのが良いでしょう。

●ビットストリームを再生成する手順

前章で作成したディープラーニングのVHDLをビットストリームに埋め込むには次の手順で進めます。

1.

このアーカイブを開いて解凍する

2.

Vivado 2014.1で先ほど生成したxillidemoプロジェクトを開く

(プロジェクトファイルはxillinux-eval-zybo-1.3b/verilog/vivado/xillydemo.xpr)

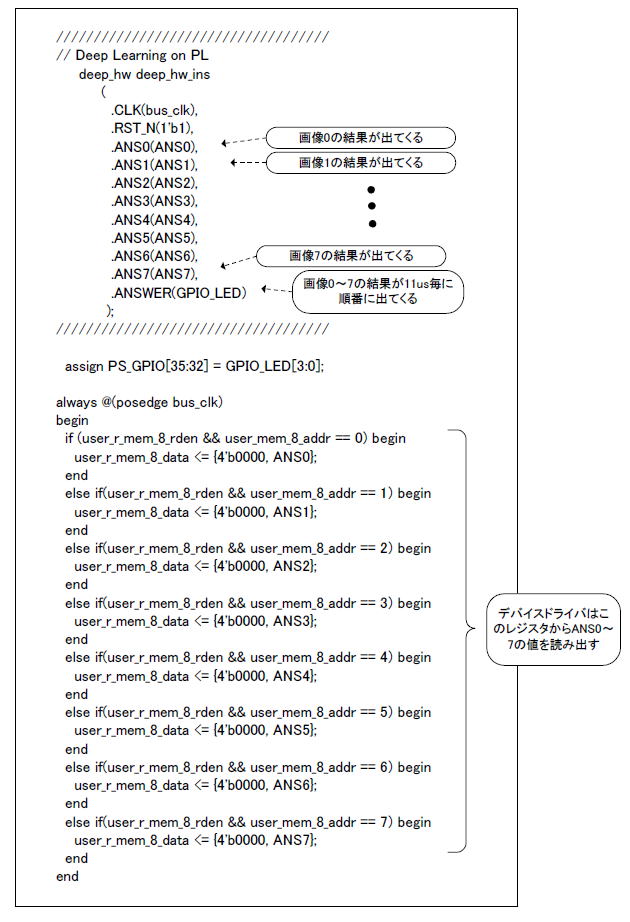

SourcesタブのHierarchyタブでxillydemoをダブルクリック

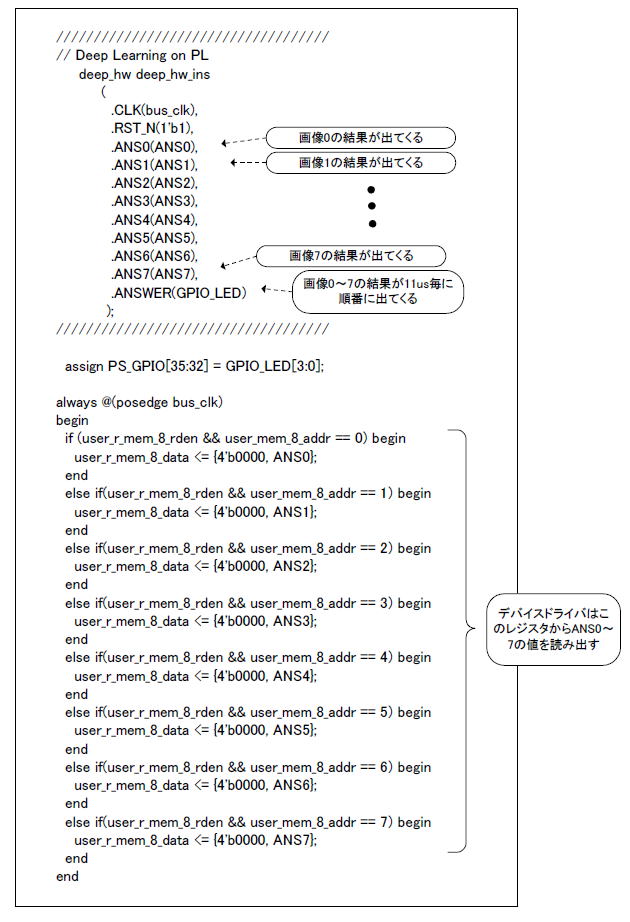

xillydemo.vの内容をアーカイブのvivado/xillydemo.vと置き換えてセーブ(リスト4-01) |

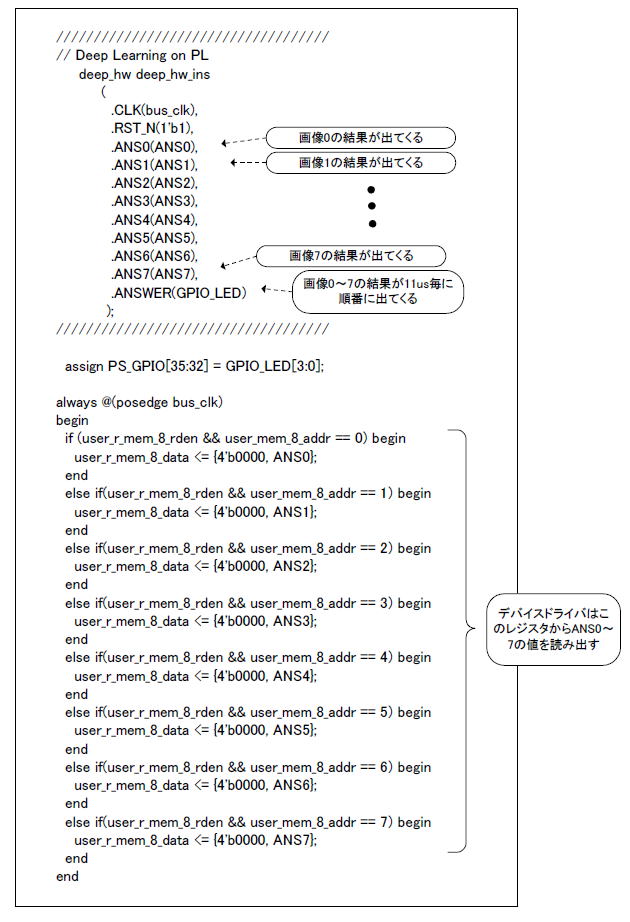

リスト4-01 xillydemo.vを置き換える

3.

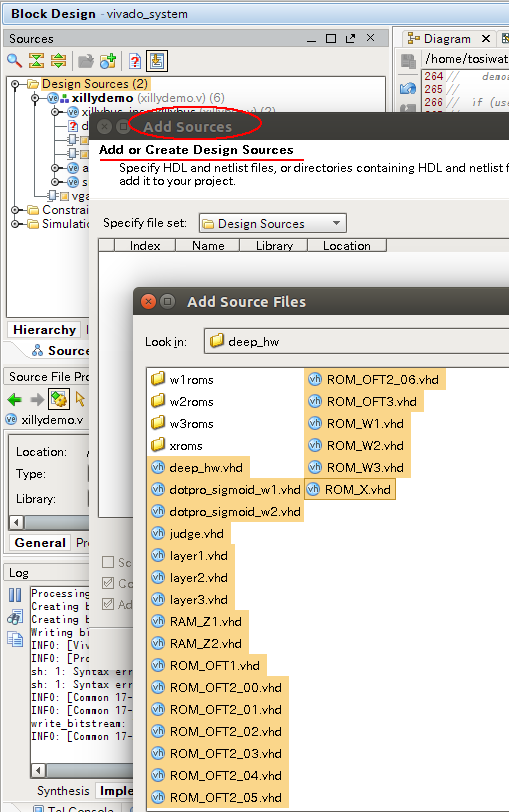

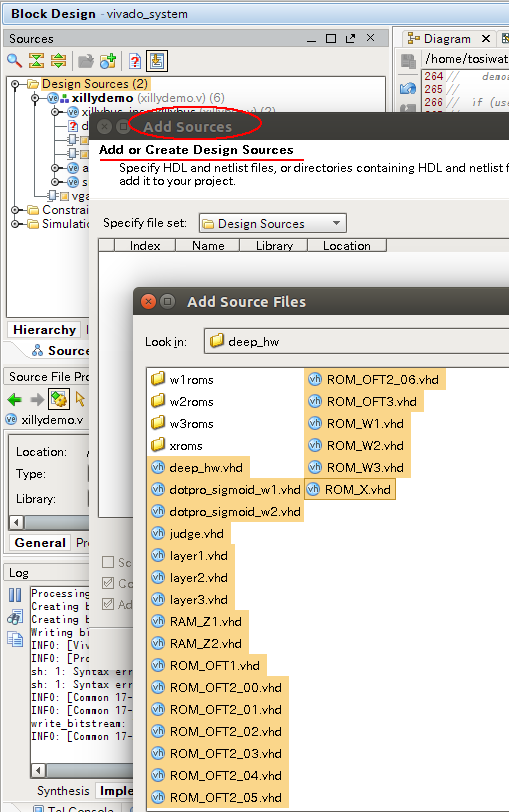

SourcesタブのHierarchyタブでDesign Sourcesを右クリック

Add sources

Add or create design sources

Add files

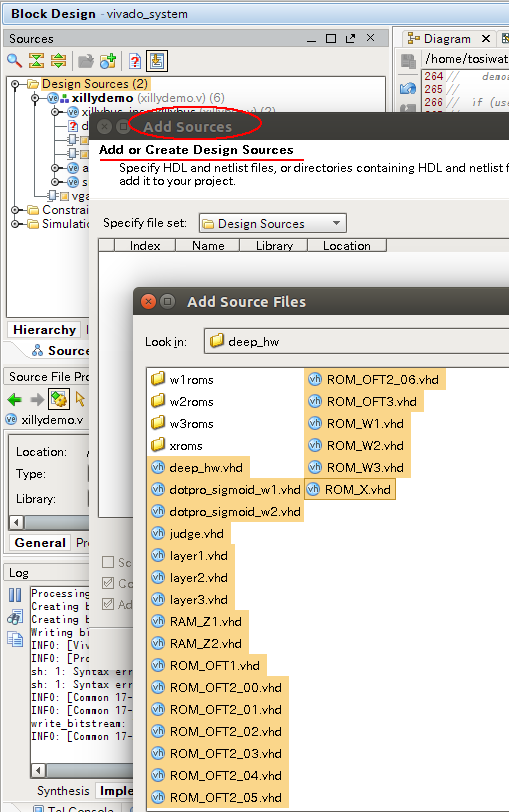

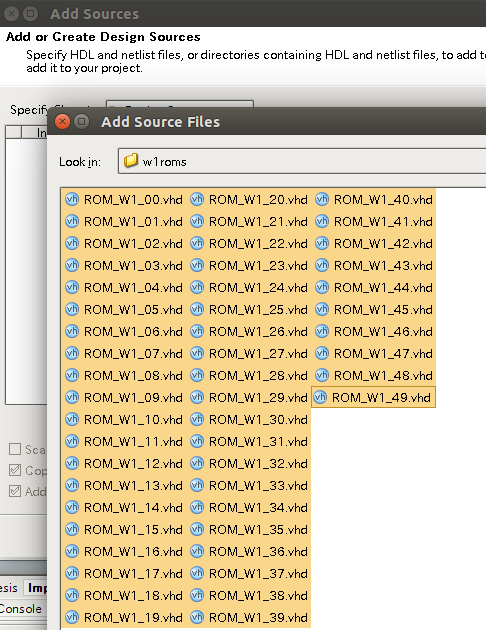

アーカイブのvivado/deep_hwディレクトリのすべてのVHDLファイルを選択してFinish(図4-05) |

図4-05 vivado/deep_hwにあるすべてのVHDLファイルをADD

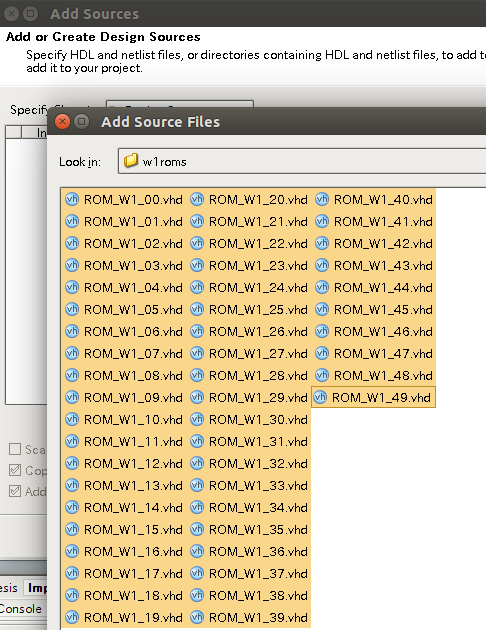

もう一度SourcesタブのHierarchyタブでDesign Sourcesを右クリック

Add sources

Add or create design sources

Add files

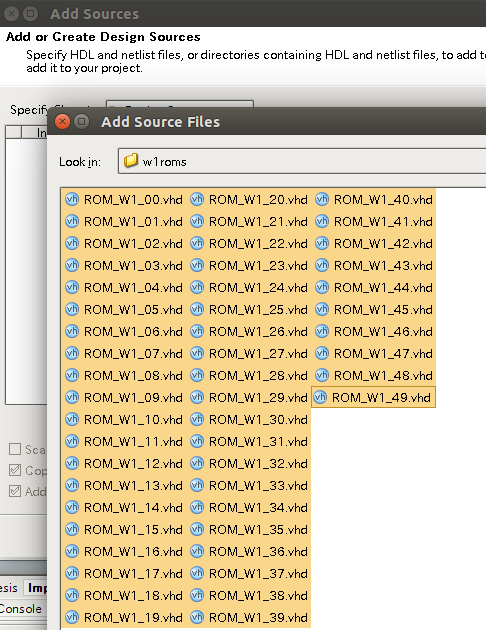

アーカイブのvivado/deep_hw/w1romsディレクトリのすべてのVHDLファイルも選択してFinish(図4-06) |

図4-06 vivado/deep_hw/w1romsにあるすべてのVHDLファイルをADD(w2roms,

w3roms, xromsも同様)

vivado/deep_hw/w2roms, w3roms, xroms以下のVHDLファイルも同様にADDしましょう。

4.

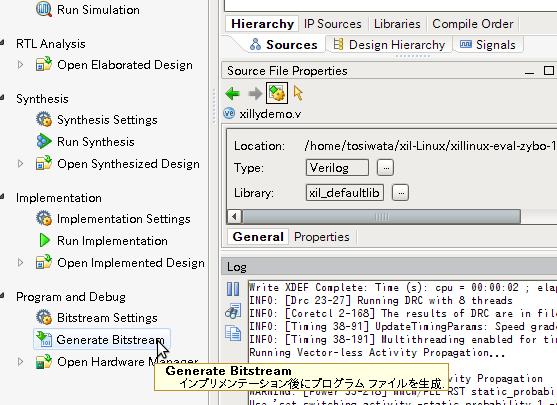

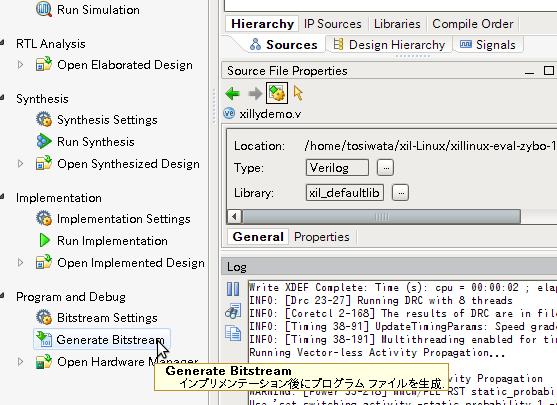

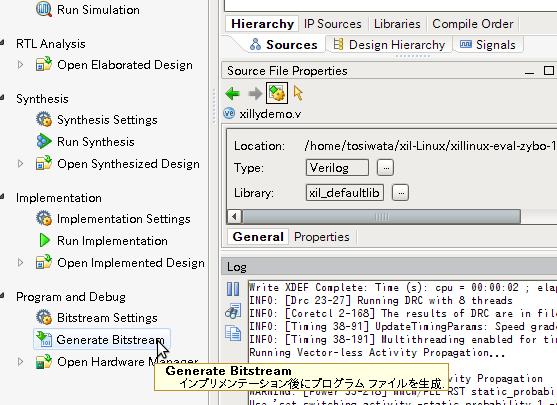

Generate Bitstreamをクリック(図4-07)

エラーなく終了したら

xillinux-eval-zybo-1.3b/verilog/vivado/xillydemo.runs/impl_1ディレクトリにxillydemo.bitが出来ているのでSDカードの同ファイルと置き換える |

図4-07 Generate Bitstreamをクリック

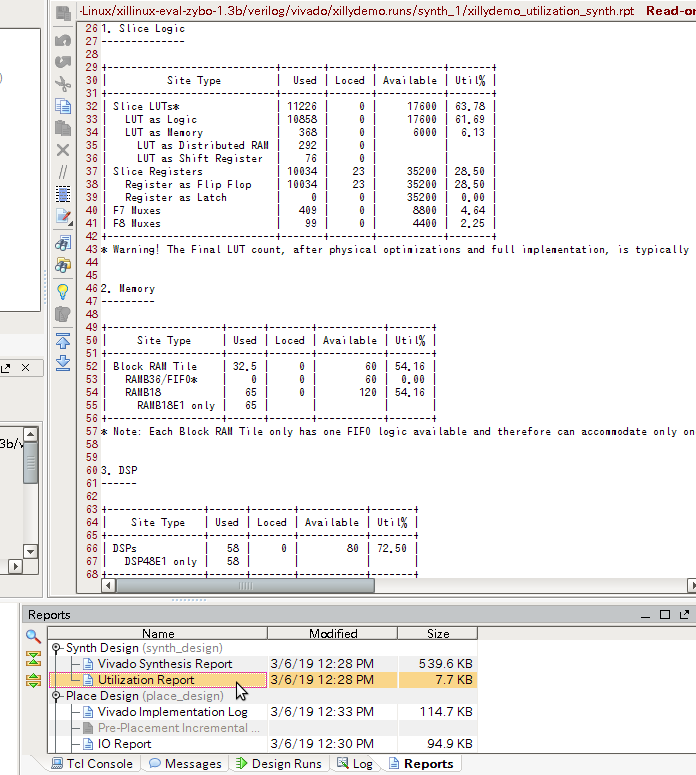

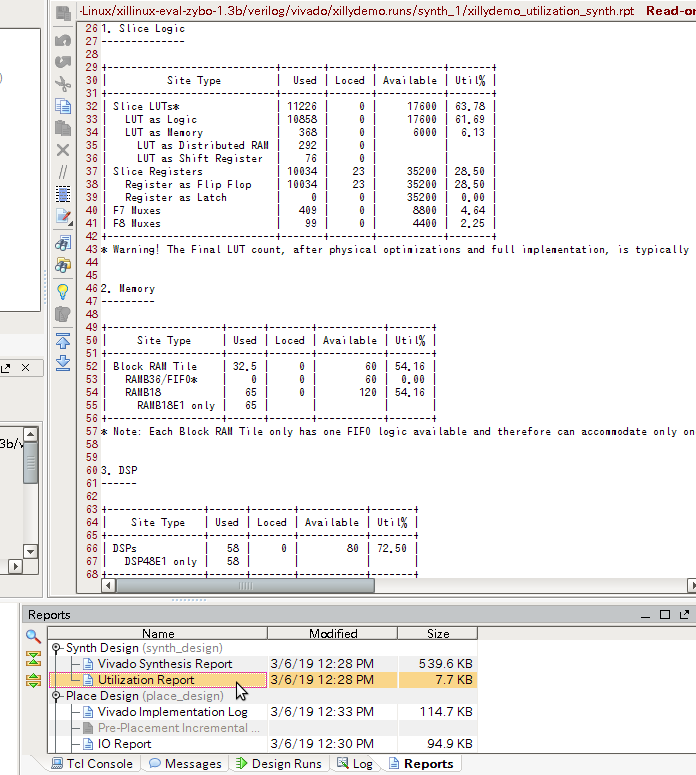

●RAMや乗算器がどれくらい使われているか確認

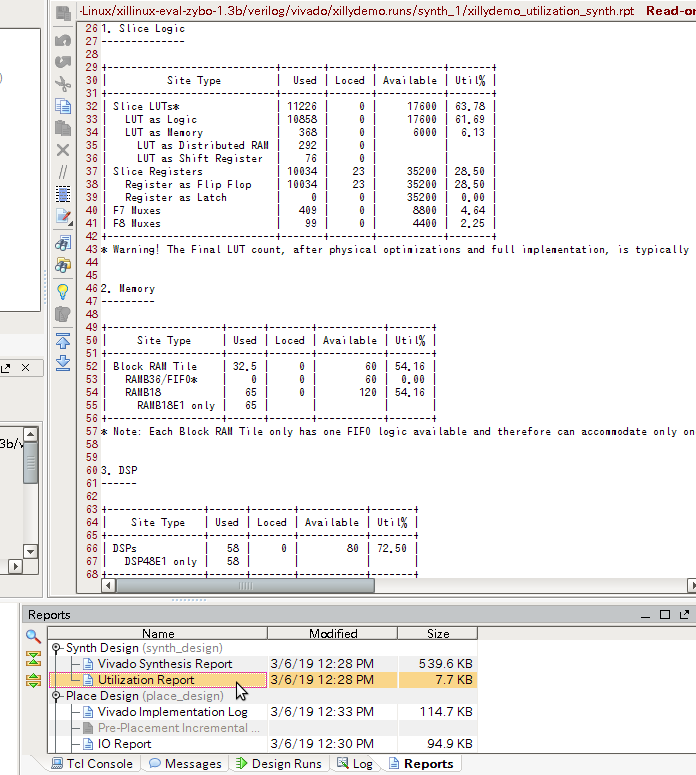

Reports→Utilization Reportをダブルクリックしましょう。LUTは63%使用しています。

Block RAMは54%の使用率です。このZynqデバイスにはRAMが全部で240kByteあるので130kByte程度の使用です。1層目の重みROMが50kByteあり、そこでの使用が一番多いようです。 |

図4-08 Reports→Utilization Reportをダブルクリック

| DSPは58個使っています。1層目で乗算器50個、2層目で7個、3層目で1個使用するので合計58個のDSPが必要になります。 |

目次へ戻る

|