コラム41 ROM/RAMに確実に割り当てられるVHDLコーディング

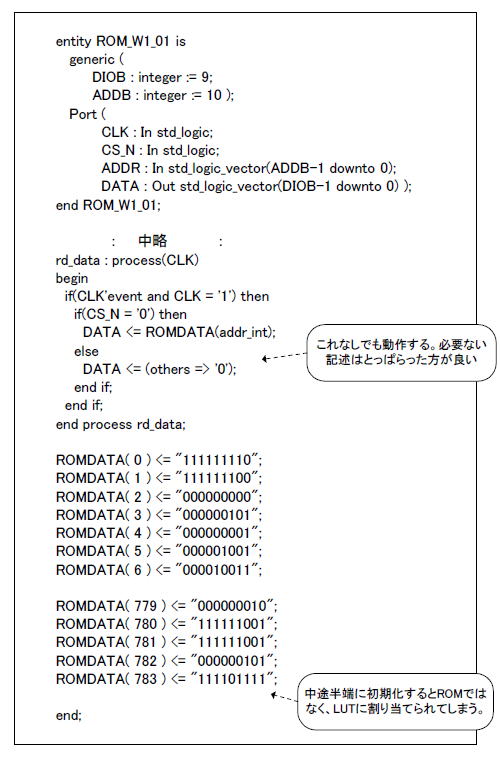

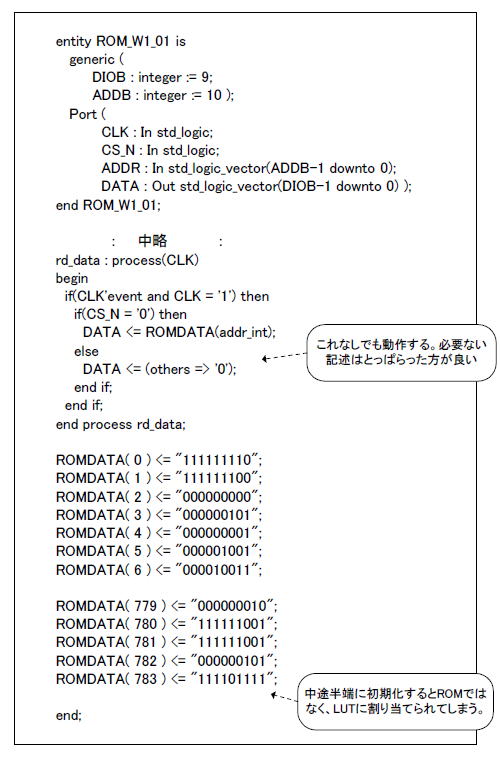

リスト4-04 悪い記述例。1層目の重みROMの部分

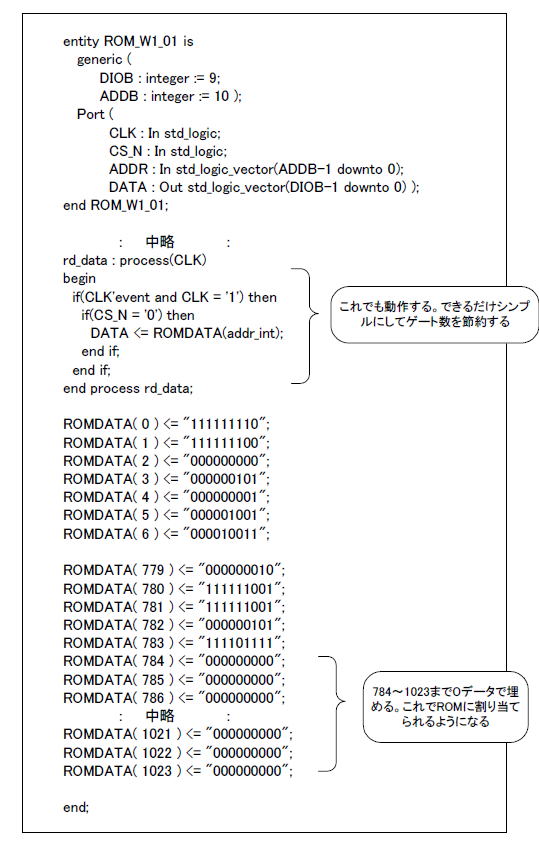

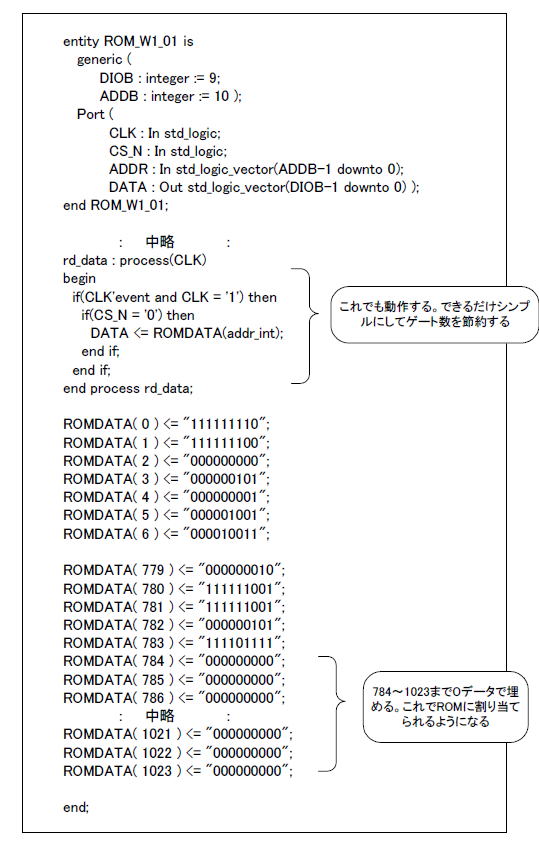

リスト4-05 良い記述例。1層目の重みROMの部分

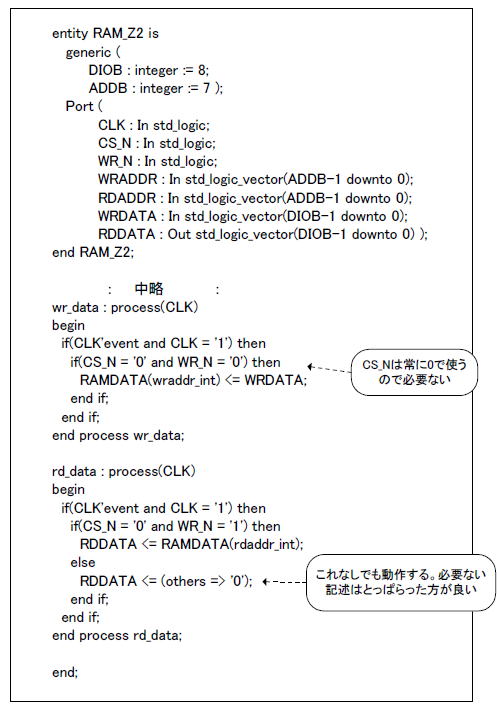

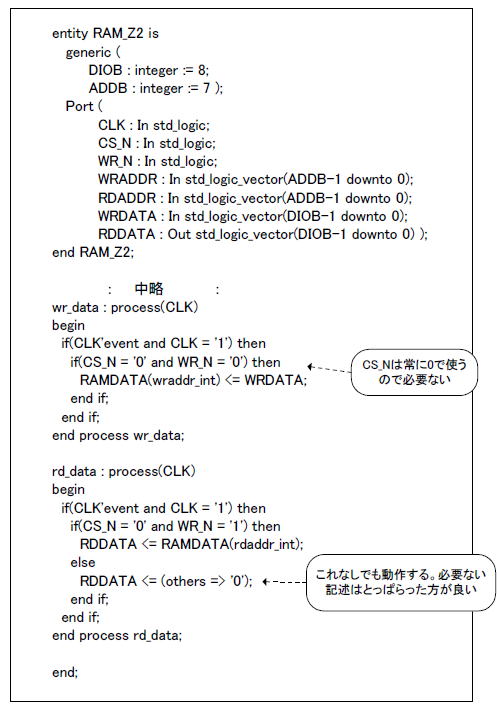

リスト4-06 悪い記述例。2層目の結果が入るRAMの部分

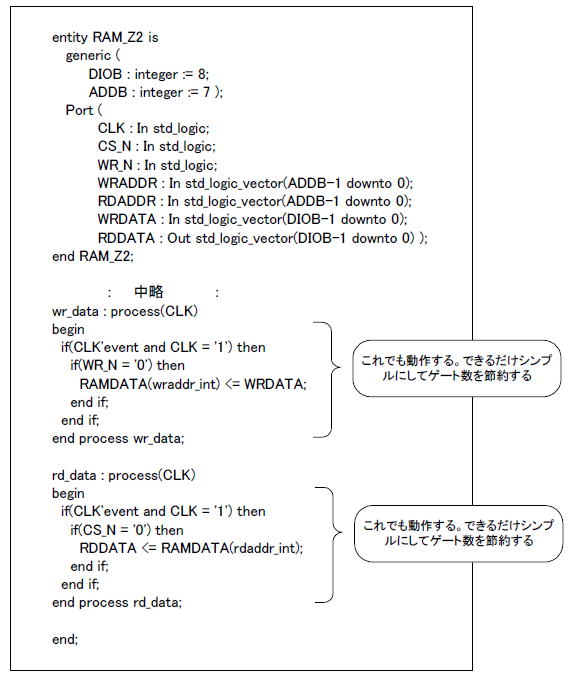

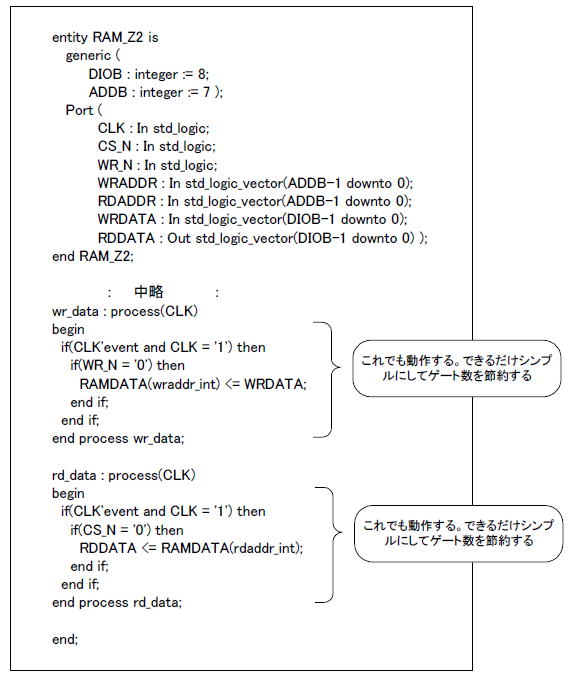

リスト4-07 良い記述例。2層目の結果が入るRAMの部分

目次へ戻る |

|||||||||||||||||

コラム41 ROM/RAMに確実に割り当てられるVHDLコーディング

リスト4-04 悪い記述例。1層目の重みROMの部分

リスト4-05 良い記述例。1層目の重みROMの部分

リスト4-06 悪い記述例。2層目の結果が入るRAMの部分

リスト4-07 良い記述例。2層目の結果が入るRAMの部分

目次へ戻る |

|||||||||||||||||