5-03 PL部の回路を変更してビットストリーム再生成

●ビットストリームを再生成する手順

ディープラーニングのVHDLをFPGAのビットストリームに埋め込むには次の手順で進めます。

1.

このアーカイブを開いて解凍する

2.

Vivado 2014.1で前章までに生成したxillidemoプロジェクトを開く

(プロジェクトファイルはxillinux-eval-zybo-1.3b/verilog/vivado/xillydemo.xpr)

SourcesタブのHierarchyタブでxillydemoをダブルクリック

xillydemo.vの内容をアーカイブのvivado/xillydemo.vと置き換えてセーブ(リスト5-01) |

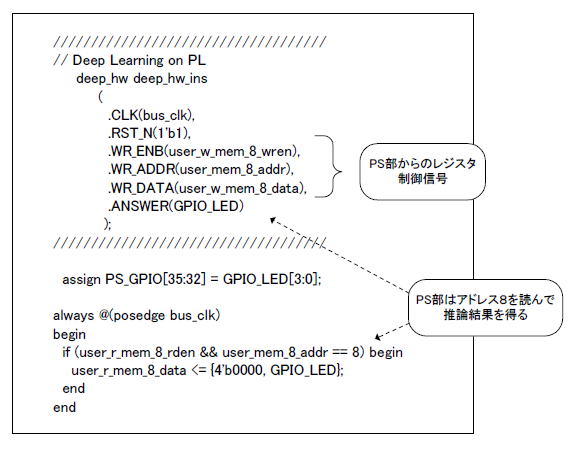

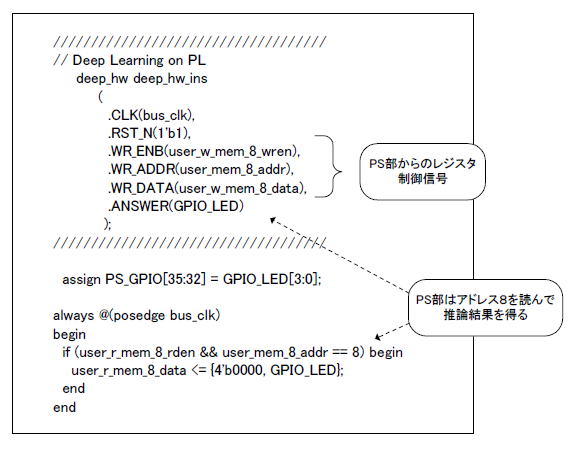

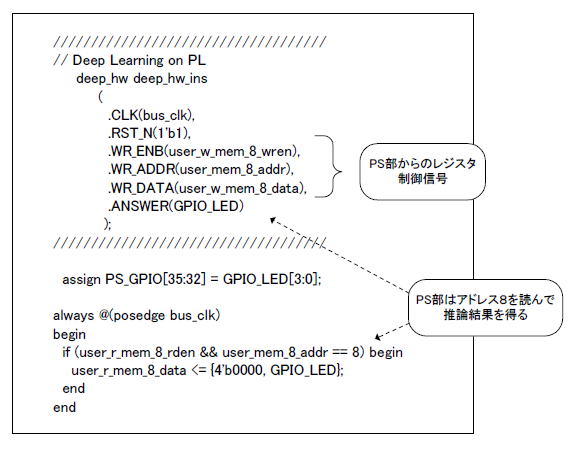

リスト5-01 xillydemo.vを置き換える

3.

SourcesタブのHierarchyタブでDesign Sourcesを右クリック

Add sources

Add or create design sources

Add files

アーカイブのvivado/deep_hwディレクトリのすべてのVHDLファイルを選択してFinish(図5-06) |

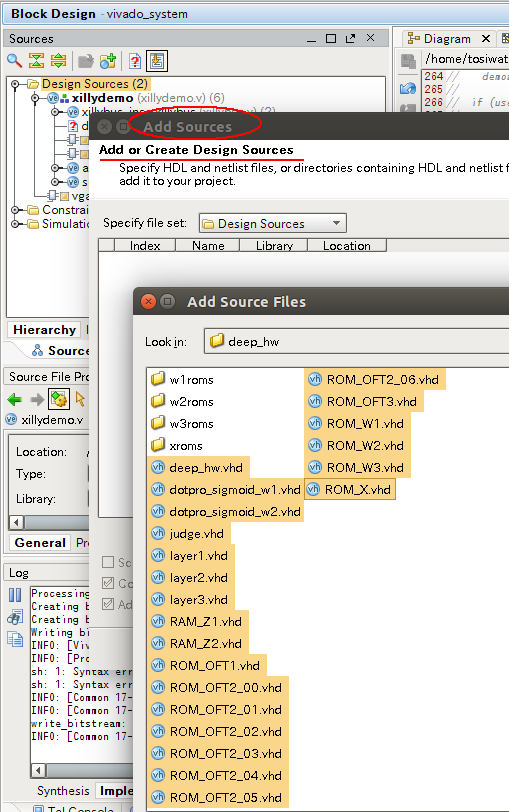

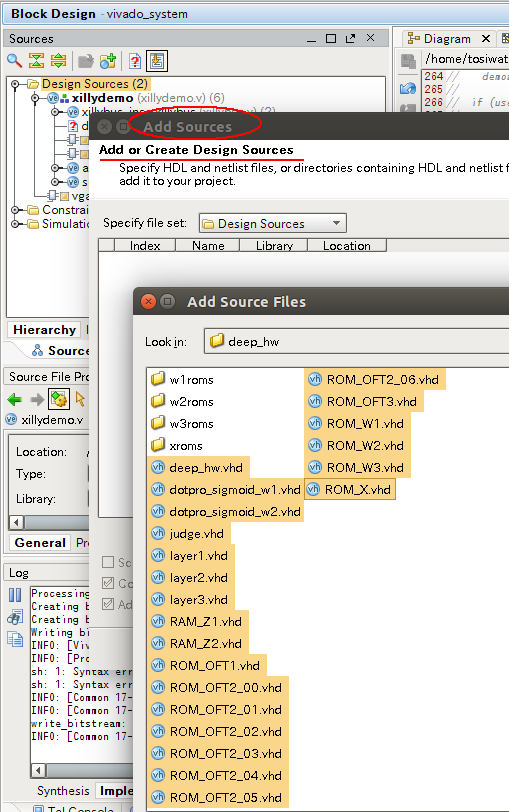

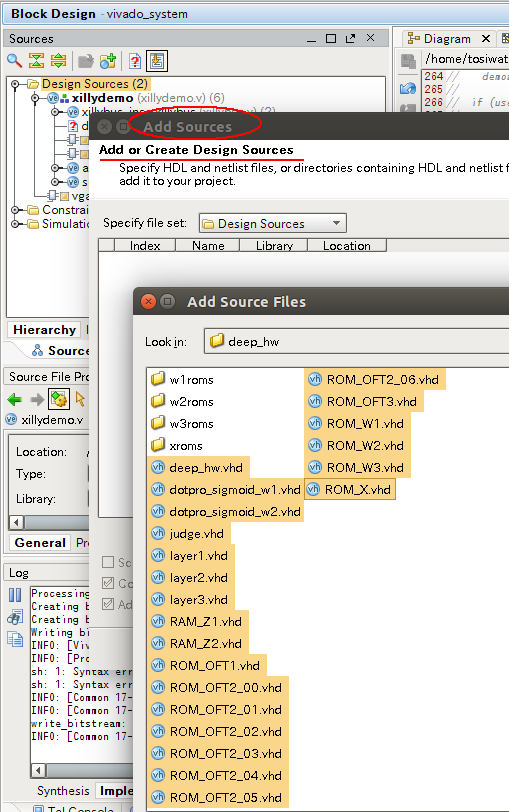

図5-06 vivado/deep_hwにあるすべてのVHDLファイルをADD

もう一度SourcesタブのHierarchyタブでDesign Sourcesを右クリック

Add sources

Add or create design sources

Add files

アーカイブのvivado/deep_hw/w1romsディレクトリのすべてのVHDLファイルも選択してFinish(図5-07) |

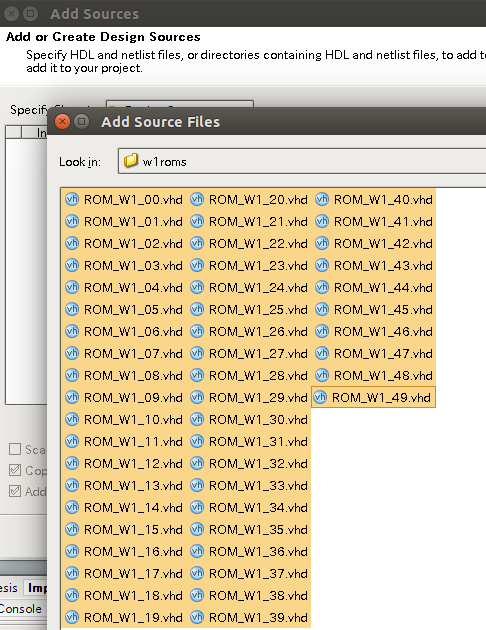

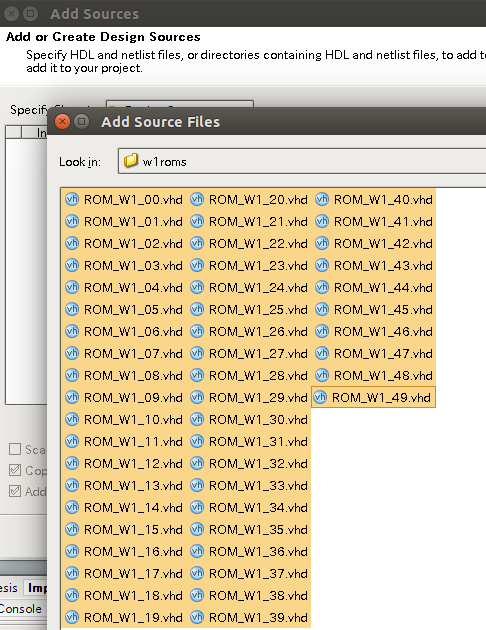

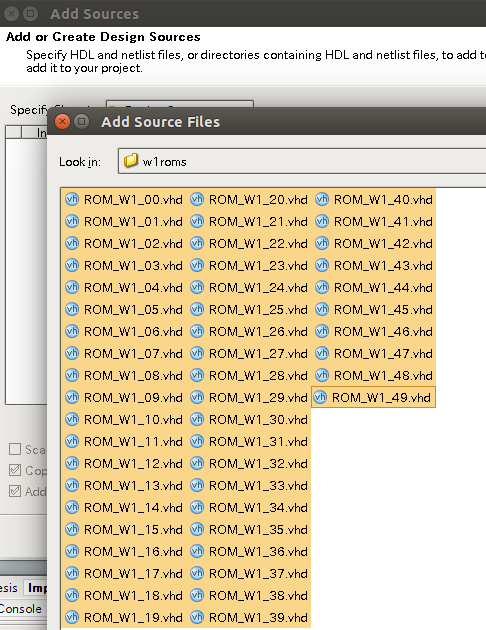

図5-07 vivado/deep_hw/w1romsにあるすべてのVHDLファイルをADD(w2roms,

w3romsも同様)

vivado/deep_hw/w2roms, w3roms以下のVHDLファイルも同様にADDしましょう。

4.

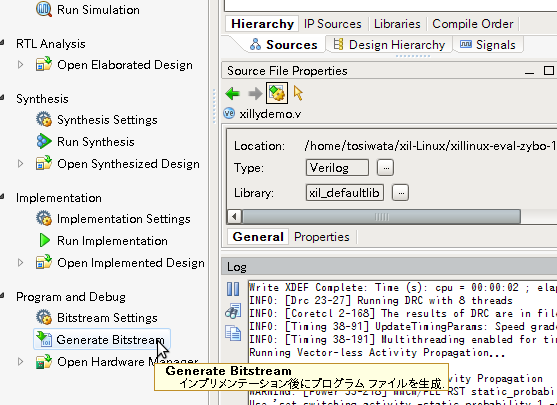

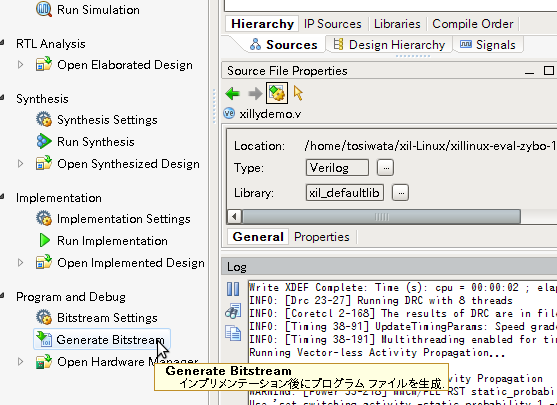

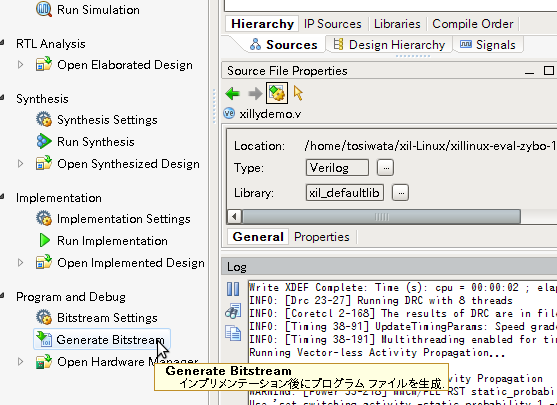

Generate Bitstreamをクリック(図5-08)

エラーなく終了したら(*2)

xillinux-eval-zybo-1.3b/verilog/vivado/xillydemo.runs/impl_1ディレクトリにxillydemo.bitが出来ているのでSDカードの同ファイルと置き換える

(*2)Timing constraints weren't met. Please check your design. というエラーが出た場合の対処は次の通り。

メニューのTools→Project Settings Implementation Optionの下の方、Rout

Designにあるtcl.postのxマークをクリックしてtclファイルを消して再度Run Implementationしてみましょう。 |

図5-08 Generate Bitstreamをクリック

目次へ戻る

|