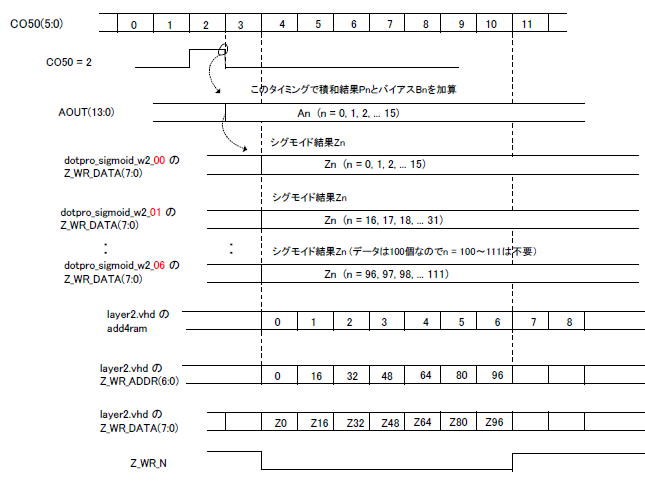

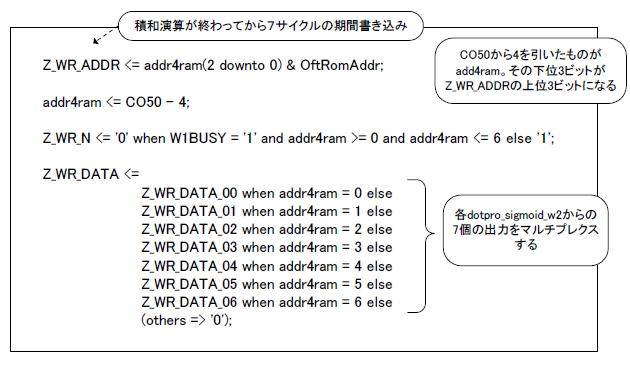

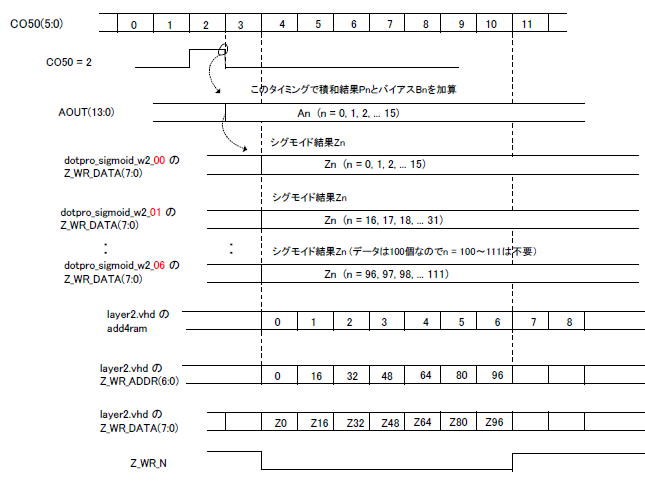

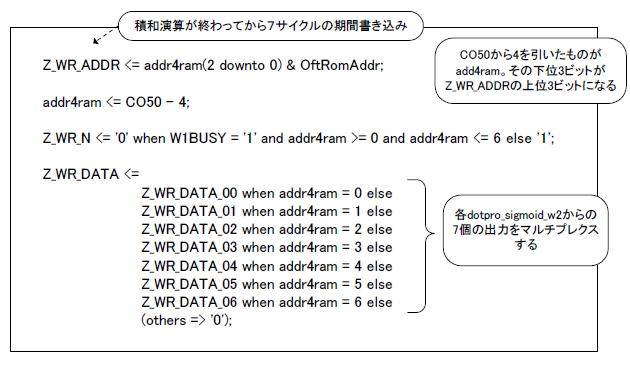

●2層目の結果をRAMに溜め込む部分

1層目の重み行列は50×100なので乗算結果は100個です。それらは7つのグループに分けられて並列に計算されます(図3-25のシグモイド結果Z0,

Z1, ... Z99)。それらはマルチプレクサで多重化されます(Z_WR_DATA、下から2段目)。

2層目の結果(Z0, Z1, ... Z99)はいったんRAMに書き込まれます。図3-25のようにRAMの書き込みアドレスZ_WR_ADDRと、書き込みイネーブルZ_WR_Nを生成します。

書き込みアドレスは同図Z_WR_ADDRのように0, 16, 32, ... 96となります。次のシーケンスでは1,

17, 33, ... 97、このシーケンスを16回繰り返して終了です。 |