丂僨傿乕僾儔乕僯儞僌偵偼乽慡寢崌僯儏乕儔儖僱僢僩儚乕僋乿傗乽忯傒崬傒僯儏乕儔儖僱僢僩儚乕僋乿偲偄偭偨庤朄偑偁傝傑偡丅戞1晹偱偼慜幰傪僴乕僪僂僄傾壔偟傑偟偨偑丄戞2晹偱偼屻幰偵挧愴偟傑偡丅

仠戞1晹偱FPGA偵幚憰偟偨偺偼乽慡寢崌僯儏乕儔儖僱僢僩儚乕僋乿

丂戞1晹偱偼28亊28夋慺傪1楍偵暲傋偰僯儏乕儔儖僱僢僩儚乕僋偵擖椡偟丄784屄慡夋慺偱愊榓傪偲偭偰偄傑偟偨丅偙偺庤朄傪乽慡寢崌僯儏乕儔儖僱僢僩儚乕僋乿偲偄偄傑偡丅

仠慡寢崌僯儏乕儔儖僱僢僩儚乕僋偺栤戣揰

丂偟偐偟偙偺庤朄偱偼丄尦乆2師尦偱偁傞夋憸偑1師尦偵暲傃懼偊傜傟偰偟傑偆偨傔丄乽廲曽岦偺夋慺僨乕僞偺娭學惈乿偑幐傢傟偰偟傑偄傑偡丅偮傑傝丄乽夋慺僨乕僞偺2師尦揑側宍忬偑柍帇偝傟傞乿偲偄偆栤戣揰偑偁傝傑偡丅

仠3亊3偺夋慺僨乕僞偲僼傿儖僞學悢傪忯傒崬傓

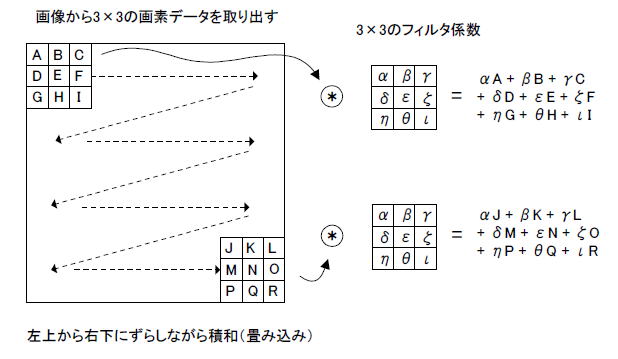

丂偦偙偱2師尦偺夋憸偺傑傑墘嶼傪峴偆偙偲傪峫偊傑偡丅堦椺偲偟偰丄夋憸偐傜3亊3偺夋慺僨乕僞傪庢傝弌偟丄3亊3偺僼傿儖僞學悢偲偺愊榓傪偲傝傑偡丅

丂偦偺張棟傪恾6-01偺傛偆偵丄夋憸偺嵍忋偐傜塃壓偵偐偗偰丄3亊3偺僄儕傾傪偢傜偟側偑傜懕偗傑偡丅偙偺堦楢偺強嶌傪乽忯傒崬傒乿偲偄偄傑偡丅

丂丂恾6亅01丂夋憸偵偍偗傞忯傒崬傒

仠夋慺僨乕僞偺宍忬傪峫椂偵擖傟偨乽忯傒崬傒僯儏乕儔儖僱僢僩儚乕僋乿

丂僯儏乕儔儖僱僢僩儚乕僋偺嵟弶偺憌傪偙偺傛偆側乽忯傒崬傒憌乿偲偡傟偽丄乽夋慺僨乕僞偺2師尦揑側宍忬乿傪悇榑偵斀塮偝偣傞偙偲偑偱偒丄偝傜側傞惓夝棪偺岦忋偑朷傔偦偆偱偡丅偙偺傛偆側庤朄傪乽忯傒崬傒僯儏乕儔儖僱僢僩儚乕僋乿偲偄偄傑偡丅

仠墘嶼検偑懡偄偺偱FPGA壔偺嵺偼岺晇偑昁梫

丂乽慡寢崌僯儏乕儔儖僱僢僩儚乕僋乿偵斾傋偰乽忯傒崬傒僯儏乕儔儖僱僢僩儚乕僋乿偼傛傝戝検偺愊榓墘嶼偑昁梫偵側傝傑偡丅戞2晹偱偼墘嶼偺暲楍壔丒僷僀僾儔僀儞壔偵傛傝崅懍壔傪恾傝傑偡丅傑偨FPGA偵幚憰壜擻偵側傞傛偆丄夞楬偺娙棯壔傕専摙偟傑偡丅

丂側偍戞2晹偱偼丄偙偺彂愋偺242儁乕僕偵偁傞忯傒崬傒僯儏乕儔儖僱僢僩儚乕僋傪戣嵽偵僴乕僪僂僄傾壔傪恾傝傑偡丅 |