8-08丂係丆俆丆俇憌栚偺夋憸偺撉傒弌偟丒彂偒崬傒

仭4憌栚偺撉傒弌偟

仠擖椡夋憸傪撉傒弌偡僔乕働儞僗傪峫偊傞

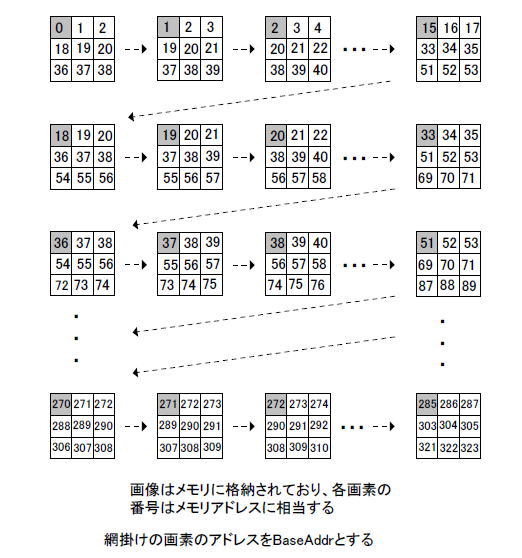

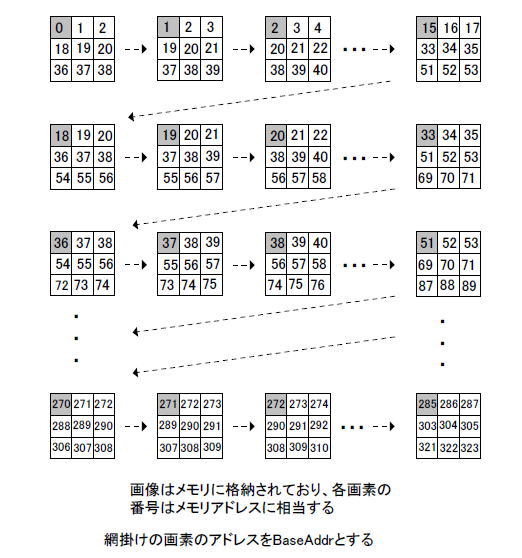

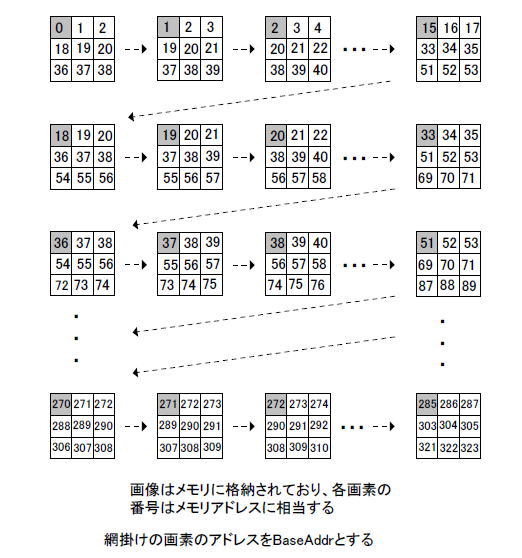

丂4憌栚偺擖椡夋慺悢偼14亊14偱偡偑丄僷僨傿儞僌偑巤偟偰偁傞偺偱丄恾8-104偺傛偆偵18亊18夋慺偑儊儌儕偵拁偊偰偁傝傑偡(擖椡僷僨傿儞僌偺暆偼俀乯丅摨恾偺傛偆偵3亊3夋慺傪庢傝弌偟偰學悢偲忔嶼偟傑偡丅奺悢帤偑偦偺夋慺偺儊儌儕傾僪儗僗偱偁傝丄栐妡偗偺夋慺傪BaseAddr偲屇傃傑偡丅 |

丂丂恾8-104丂3亊3夋慺偺撉傒弌偟僔乕働儞僗

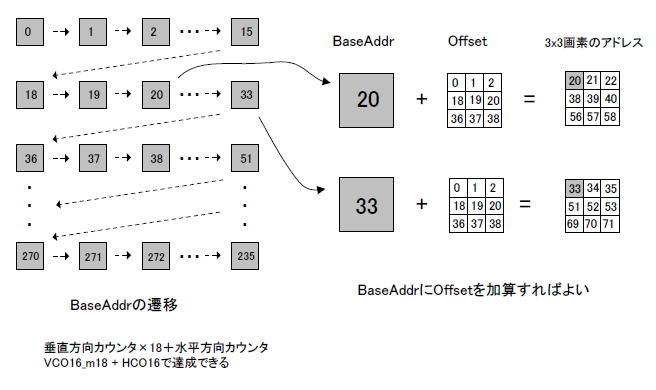

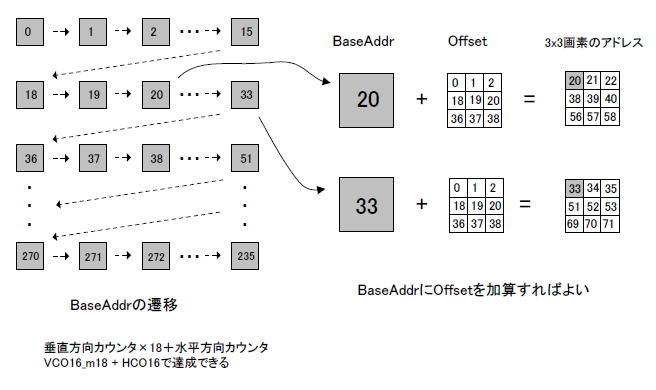

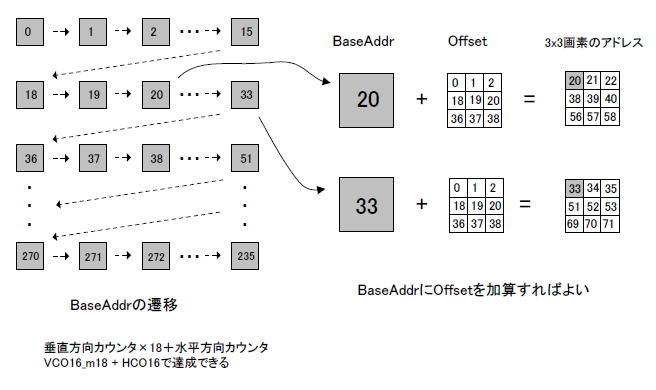

仠BaseAddr偵Offset傪懌偣偽椙偄

丂BaseAddr偼恾8-105偺嵍偺傛偆偵慗堏偟傑偡丅傎偐偺夋慺偼摨恾塃偺傛偆偵BaseAddr偵偁傞寛傑偭偨抣乮Offset偲屇傇乯傪壛嶼偡傟偽偦傟偧傟偺傾僪儗僗偑摼傜傟傞偙偲偑暘偐傝傑偡丅 |

丂丂恾8-105丂撉傒弌偟傾僪儗僗偺嶌傝曽

仭4憌栚偺彂偒崬傒

仠僷僨傿儞僌傪巤偟偨忬懺偱RAM偵彂偄偰偍偔偲師偺憌偱妝

丂4憌栚偺弌椡偼16亊16夋慺偱偡偑丄偦傟偵僾乕儕儞僌傪巤偟偰8亊8夋慺偲側偭偰弌椡偝傟傑偡丅

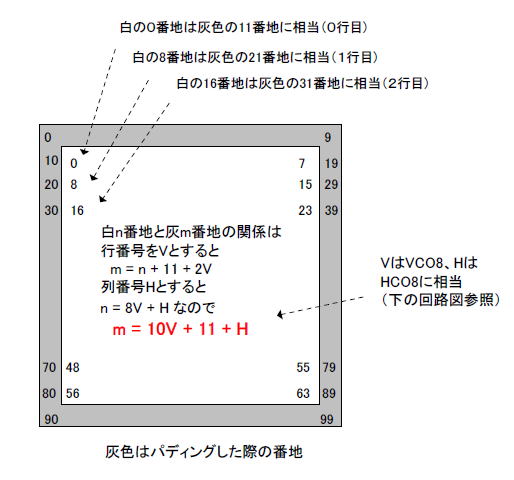

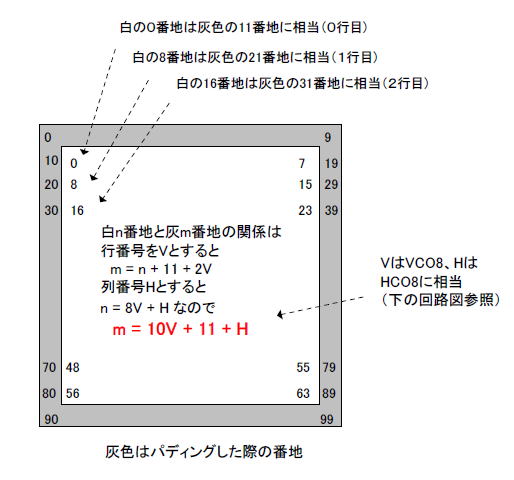

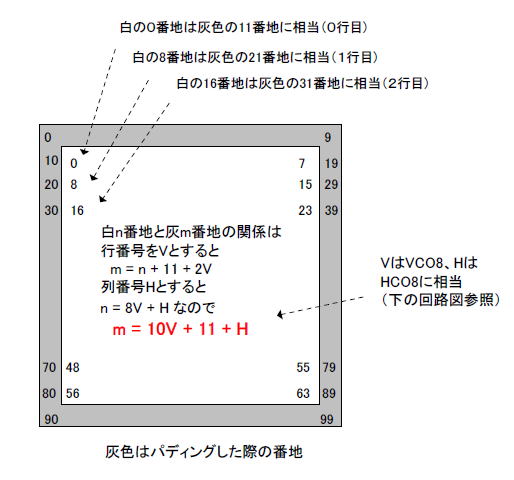

丂恾8-106偺敀偺晹暘偼8亊8偺夋憸丄奃怓偺榞偼偦傟偵僷僨傿儞僌傪巤偟偰10亊10偺夋憸偵偟偨傕偺偱偡丅敀偺夋憸偵偼0乣63傑偱斣崋偑晅偗傜傟偰偄傑偡丅偙偺斣崋傪n斣抧偲屇傇偙偲偵偟傑偡丅

丂傑偨奃怓偺夋憸偵偼0乣99傑偱斣崋偑晅偗傜傟偰偍傝丄偙偺斣崋傪m斣抧偲屇傇偙偲偵偟傑偡丅 |

丂丂恾8-106丂師偺憌偺偨傔偵僷僨傿儞僌偟偰彂偒崬傓

丂m偲n偺娭學偼摨恾偺傛偆偵丄m = 10V + 11 + H 偲側傝傑偡丅偙偙偱V偲偼廲曽岦8恑僇僂儞僞(VCO8)偺抣丄H偼墶曽岦8恑僇僂儞僞(HCO8)偺抣偱偡丅

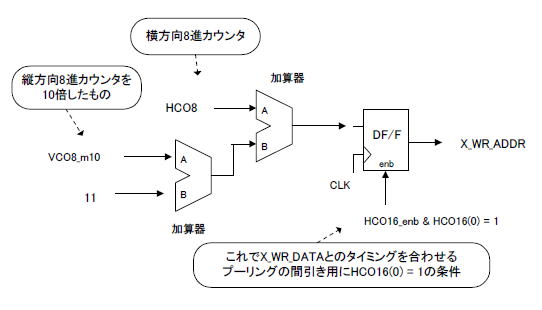

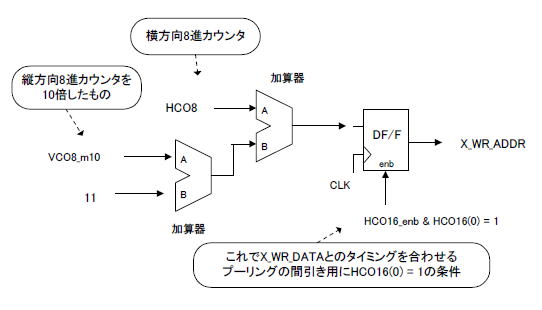

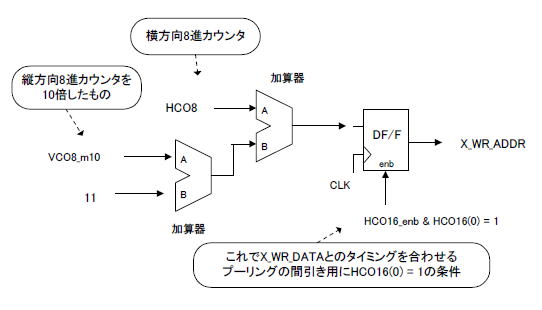

丂偟偨偑偭偰恾8-107偺傛偆側夞楬偱夋憸RAM偺彂偒崬傒傾僪儗僗傪惗惉偱偒傑偡丅僾乕儕儞僌偺娫堷偒傪娪傒偰HCO16(0)=1偲偄偆忦審傪壛偊偰儔僢僠偟傑偡丅 |

丂丂恾8-107丂彂偒崬傒傾僪儗僗惗惉夞楬

師偺儁乕僕傊

栚師傊栠傞 |