13-02 CMOSカメラの動画をVGAに映すにはSDRAMが必須

●ARM部は使わない。ロジック部だけで処理する

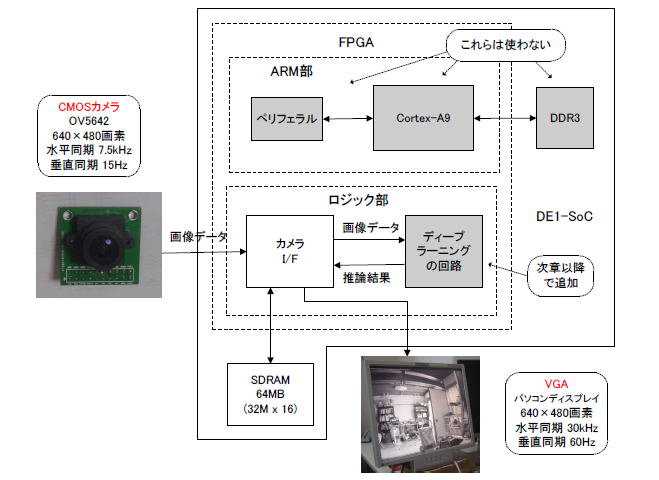

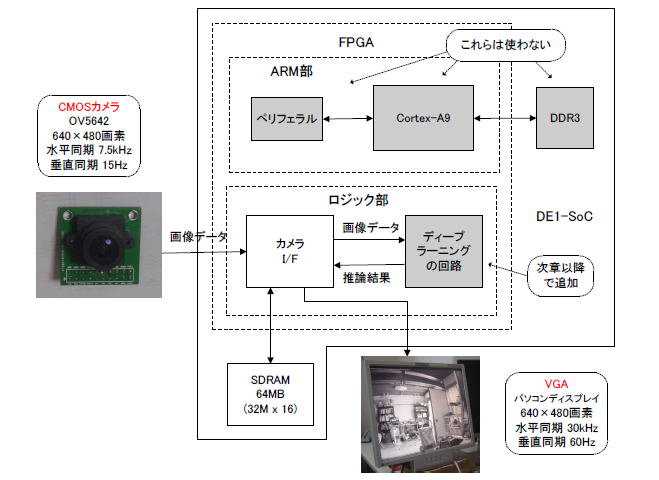

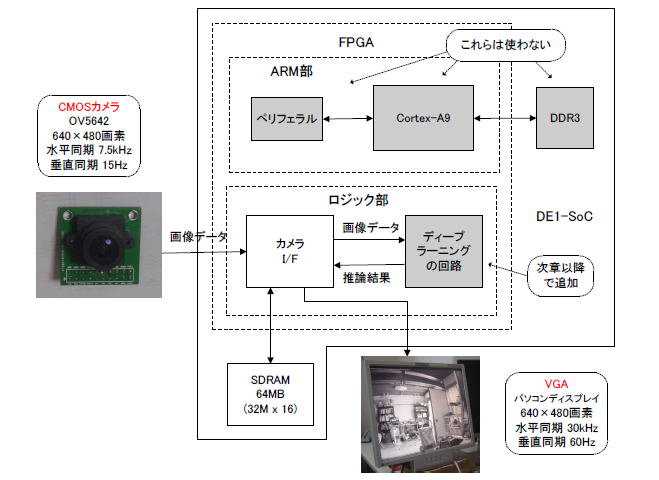

DE1-SoC搭載のFPGA(CycloneV)には図13‐01のようにARMプロセッサ(Cortex-A9)が内蔵されていますが、今回それは使用しません。

CMOSカメラはロジック部のみで処理され、VGAに動画が映されます。同図にはディープラーニングの回路がありますが、これは次章以降で追加します。 |

図13-01 全体のブロック図。今回はとりあえず動画を映すだけ

●波長が合わない二人

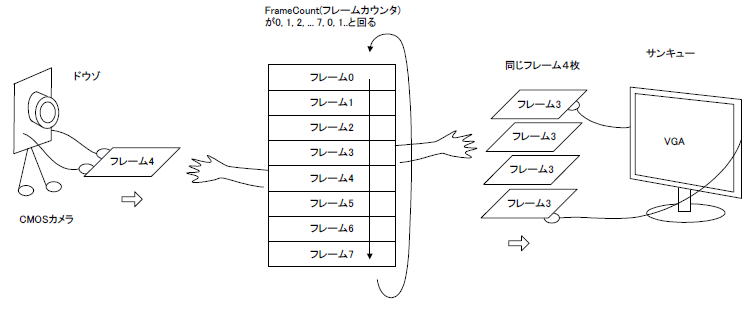

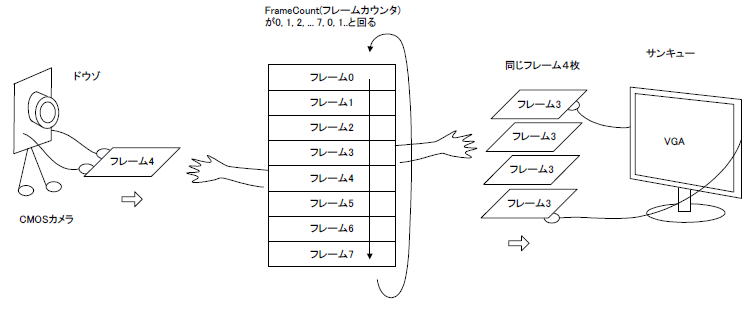

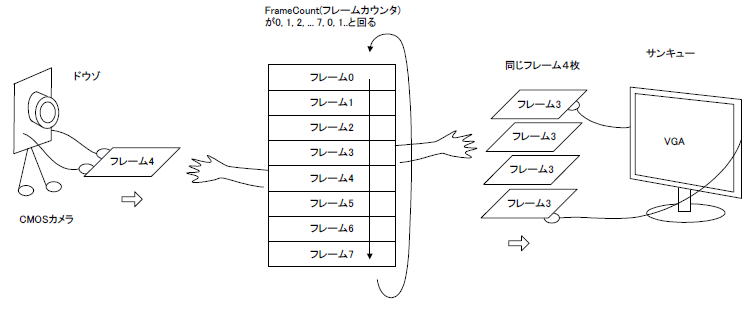

CMOSカメラの動画をVGAに映すにはSDRAMが必須になります。なぜかというと、双方の同期信号が異なるため(図13‐02)直接やり取りすることはできず、SDRAMが間に入ってあげる必要があるからです。 |

図13-02 誰かが間に入ってあげないと…

●ロジック部から操作できるSDRAMがある!

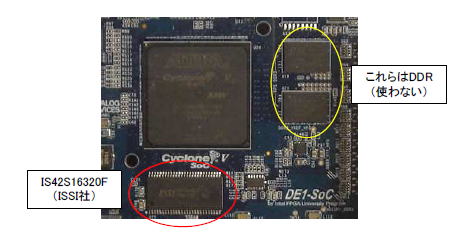

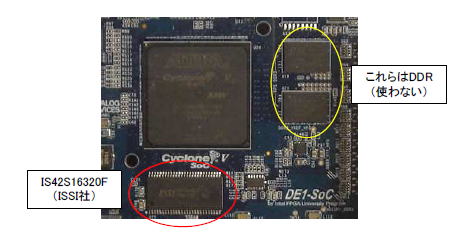

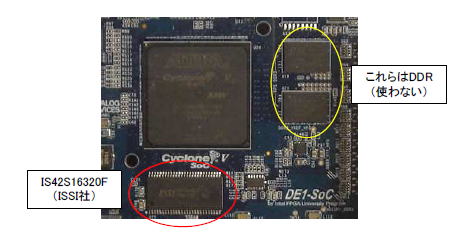

DE1-SoCにはSDRAMが搭載されているため(図13‐03の赤丸)、それを活用します。容量は64MB、データ幅が16ビット、アドレス空間が32Mです。 |

図13-03 SDRAMは32MBと画像処理に十分使える容量

●読み方は書き方の後をぐるぐる追いかける

SDRAMの中に8フレームぶんの領域を設け、図13‐04のようにCMOSカメラ画像をフレーム0〜7にぐるぐる書き込みます。VGAはその前のフレームを追いかけます。

VGAの垂直同期周波数(60Hz)はカメラのそれ(15Hz)の4倍なので、同じ画像を4回読んで表示します。このようにしてCMOSカメラと垂直同期をとります。 |

図13-04 同じ画像を4回映して同期をとる

●水平同期は内部RAM、垂直同期は外部RAMを使う

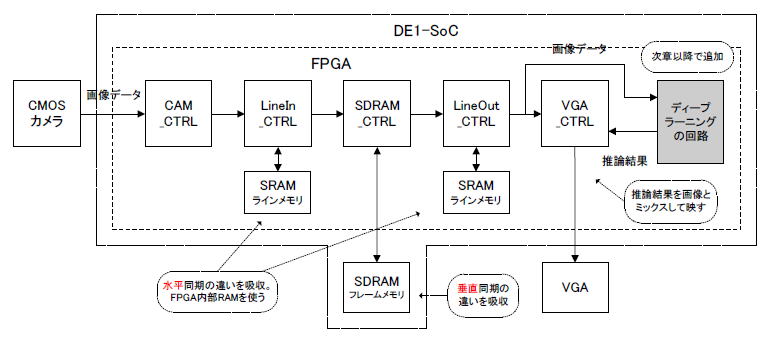

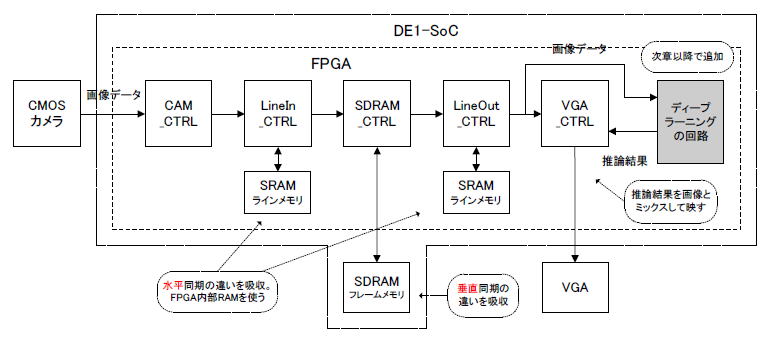

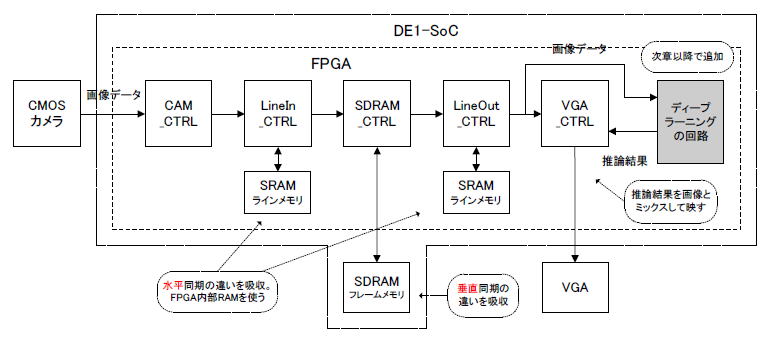

図13‐01のロジック部を詳しく書いたものが図13‐05です。

LineIn_Ctrl, LineOut_Ctrlではラインメモリを用いて水平同期をとります。ラインメモリは数kBあれば十分なので、同図のようにFPGA内部RAMを使用します。

SDRAM_Ctrlではフレームメモリを用いて垂直同期をとります。フレームメモリは数MB以上必要なので、同図のように外部にあるSDRAMを使用します。 |

図13-05 フレームメモリは大容量なので外部SDRAM

●複雑な回路の実装は論理シミュレーションの後で

SDRAMに画像を読み書きするには入念なシミュレーションが必須になります。その手順に関してはこの書籍を参考にすると良いでしょう。 |

目次へ戻る |