まとめ HDLのみで行うガチガチのハードウエア推論の世界!

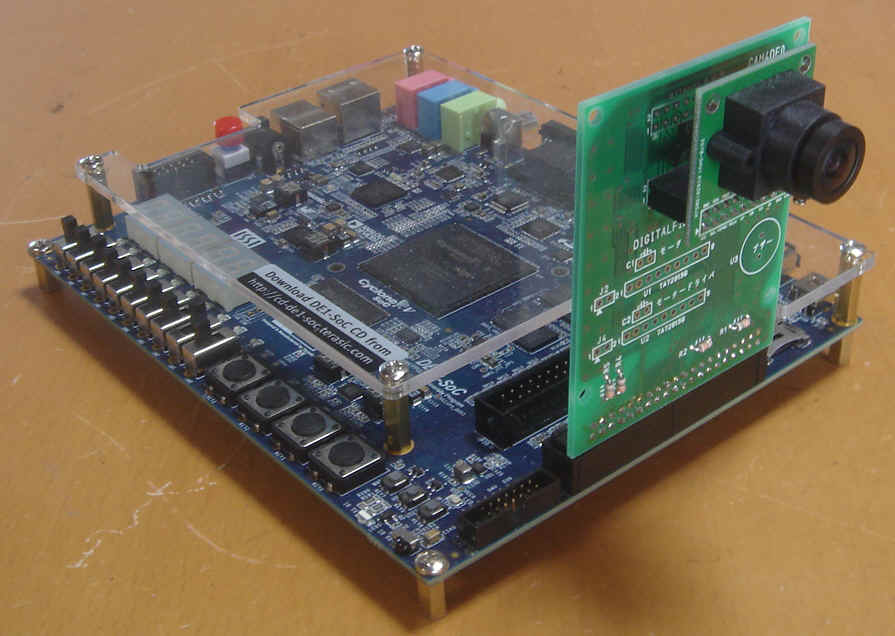

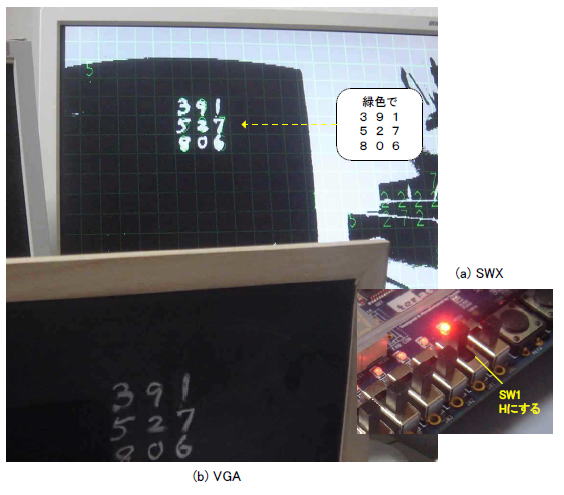

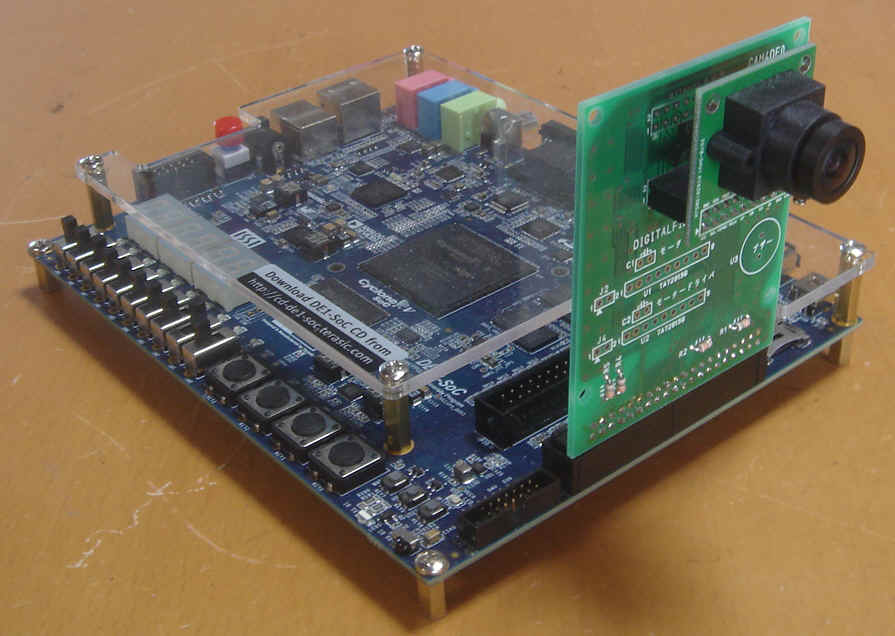

●写真14-10は完成品の外観

①FPGAボードはTerasic社のDE1-SoC(日本円で3万円弱)、Intel(旧Altera)社のCycloneVシリーズ(5CSEMA5F31C6)が搭載されています。

②CMOSカメラ(イメージセンサ)モジュールはOV5642、日昇テクノロジー社、ebay(これ以外にも複数社ある)から3~4千円で購入できます(*2)。

③アダプタボード(カメラとFPGAボードをつなぐボード)はデジタルフィルター社から3,600円で購入できます(*1)。

(*1)DE0ボード+OV7670用だが、DE1-SoC+OV5642にも使える。16ピンコネクタは日昇カメラ側に半田付け。

(*2)秋月電子にもあるが、裏に水晶発振器がないのでそのままでは使えない。 |

写真14-10 FPGAボード+アダプタボード+CMOSカメラモジュール

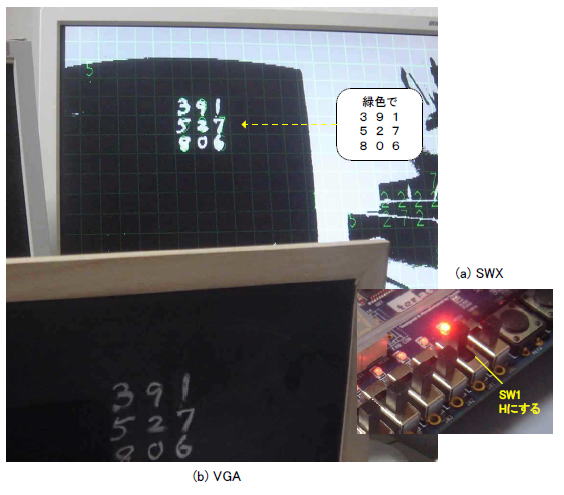

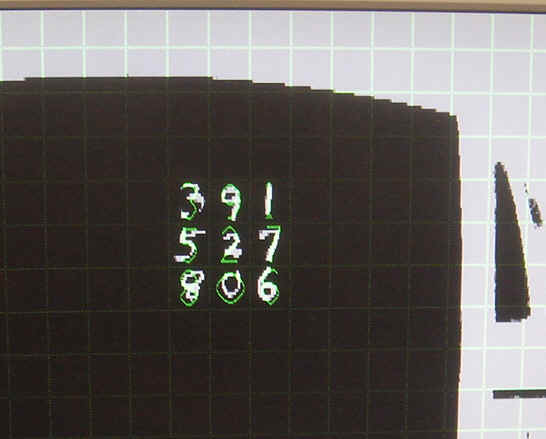

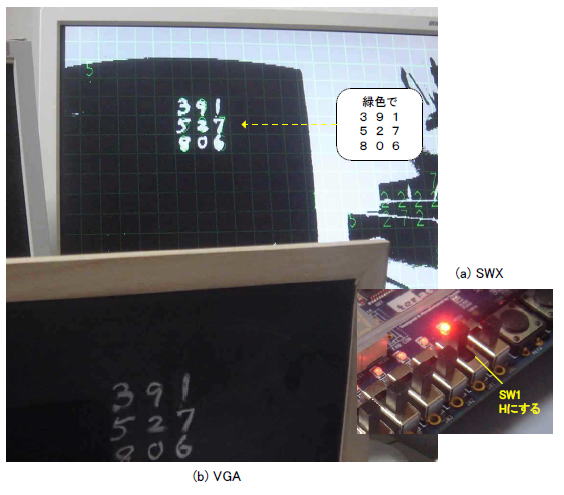

写真14-11 黒板にチョークで数字を書いてカメラの前にかざす

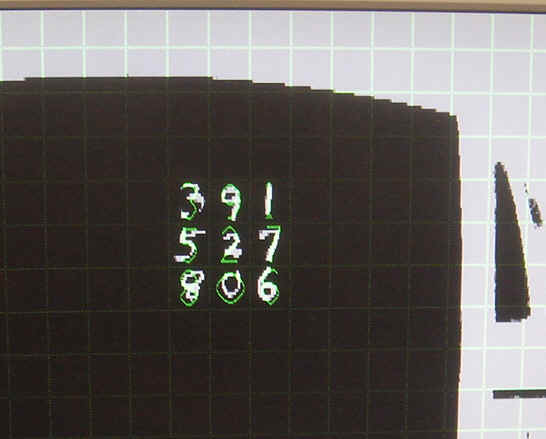

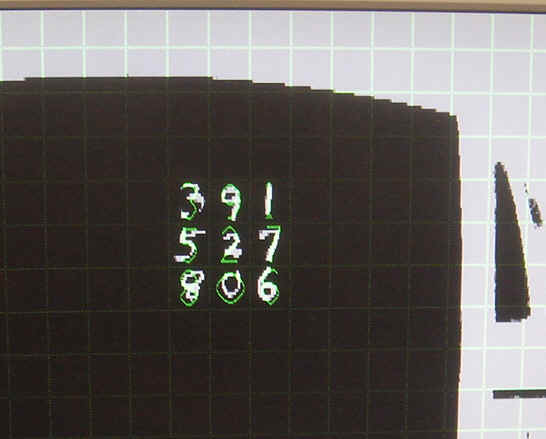

写真14-12 推論結果が重ね書きされる

●MNISTは28x28画素なのでVGAを分割して推論

FPGAボードをVGAにつなぎ、黒板にチョークで数字を書き、写真14-11, 12のようにカメラの前にかざすと推論結果が緑色で上書きされます。

VGAは640x480画素なので、28x28画素のエリアが横に23個、縦に17個存在します。それらすべてのエリアをリアルタイムに推論します。

Youtube動画1

Youtube動画2 |

●HDL(RTL, Register Transfer Level)のみで推論する

このFPGA(CycloneVシリーズ、5CSEMA5F31C6)にはCortex-A9というARMプロセッサが入っていますが、それは使用しません。

またNiosIIというソフトマクロマイコンがありますが、それはCMOSカメラのレジスタ設定にのみ使います(電源投入時に一度だけ)。

ディープラーニングの推論の部分はすべてHDLで書かれています。高位合成(HLS)は使いません。特殊なIPコアやライブラリも使いません。この書籍にある「畳み込みニューラルネットワーク」のPythonプログラムをすべて自力でHDL化しました。重み係数などは大量のHDLファイルが必要になりますが、それらはEXCEL+VBAを駆使して自動生成しています。 |

●ディープラーニングをハードウエア化(FPGAに実装)するメリット

・並列化、パイプライン化が容易

FPGA内のリソースが許す限り並列化できます。畳み込みが6層、Affineが2層、計8層ありますが、パイプライン化しているのでスループットは1層にかかるサイクル数(約10kサイクル)で済みます。

・GPUに比べて低消費電力

クロックは100MHz程度で動かすのでGPUなどに比べて低消費電力になります。放熱板もいらないので小型・軽量化が可能になります。

・高いリアルタイム性と安定性

パソコンやラズベリーパイはOSの状態によって「ある処理にかかる時間」が変動します。またOSにはフリーズやカーネルパニックの危険性が常に伴います。それに対しFPGAは「ある処理にかかる時間」を正確に見積もることができ、いかなる場合も変動しません。

・電源投入後すぐに動く即応性

自動車などはエンジンをかけてすぐに電気系統を動かす必要があります。FPGAの場合は数十msでコンフィギュレーションが終わって即動作します。

●FPGAに実装するためのポイント

本企画では畳み込みニューラルネットワーク(CNN)をHDL化してFPGAに実装しました。そのためにキーとなる技術を以下にまとめます。

①係数や変数を整数化する。

②係数を4種類にして乗算をビットシフトで達成する。

これらはFPGAに実装するために必要な技術です。

③並列化する

④パイプライン化する

これらは演算を高速化するための技術です。

⑤EXCEL+VBAでHDLを自動生成する。

これはHDL化作業を効率化するための技術です。

●キーワードは整数化と自動化と規則性

「畳み込みニューラルネットワーク」は畳み込み1~6層、その後Affine1~2層と多層にわたり複雑ですが、所詮は整数の掛け算と足し算です。言語がPythonからHDLに変わっても結果が変わる理由はありません。

また重み係数が多く、HDLファイル数が膨大になりますが、VBAなどで自動生成すればそれほど手間はかかりません。

また、各層の回路には「強い規則性」があるので、ひな形のHDLを作ってしまえば後は微調整で済みそうです。

以上のことを鑑みて皆さんも「ディープラーニングのハードウエア化」に挑戦してみてください! |

目次へ戻る |