2-07 層間にリミッタを設けてレジスタやRAMの節約

●FPGA内部RAMを使う

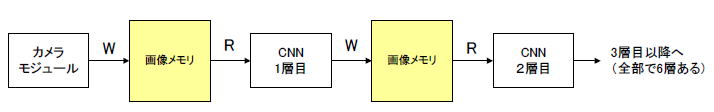

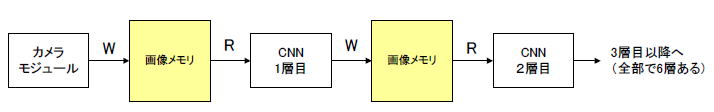

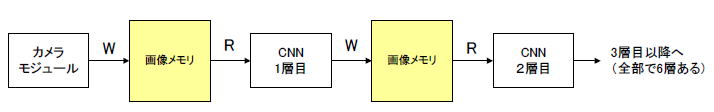

各層間のデータの受け渡しは図2‐35のようにRAM(画像メモリ)を介して行われます。これらメモリに読み書きするデータが大きい(ビット幅が多い)とFPGA内部RAMが足りなくなる恐れがあります。 |

図2-35 RAMのデータ幅を小さくしたい

●符号なし5ビットに収める

したがって図2‐36のように各層の出力にリミッタを設けます。同図では1層目の出力が31を超えないように(5ビットで収まるように)しています(*1、2)。

(*1)各層”ReLU”があるので出力は正の数のみ。リミッタで0〜31になる。

(*2)この理由で各層の出力を1/256するが、1層目は更に1/8にする。これも5ビットに収めるための対策。 |

図2‐36 Pythonコードの一部

●演算の途中経過を見てみる

また同図ではその出力をCSVファイル(lay1out_00〜15.csv)にセーブしています。図2‐37はlay1out_00.csv(1層目の出力Ch0)で、このように最大31で飽和しています。 |

図2‐37 1層目の出力。31でリミッタがかかっている

●5層目の出力も31でリミッタ

リミッタは1層目から5層目の出力に施されます。図2‐38はlay5out.csv(5層目の出力)です。全結合層なので出力チャネルは一つ、要素数は128になります。最後のデータにリミッタがかかっているのが分かります。 |

図2‐38 5層目の出力

●レジスタなど回路全体の削減に効いてくる

リミッタを設けてビット数を制限することによりRAMはもちろん、各層内で使用するレジスタ(DF/F)も削減できます。

●2〜6層目のバイアスの値を1/8に

また図2‐36のように1層目の出力は1/256の後、1/8されています。それにより2層目以降の入力のボリュームが1/8になるので、バイアスもそれに合わせて1/8にします(図2‐39) |

図2‐39 2層目以降はバイアスを1/8にする

次のページへ

目次へ戻る

|