FIRフィルタのVHDLコードについて FIRフィルタのVHDLコードについて

N次FIR フィルタの数学的モデル。"D"はD型フリップフロップで単位遅延素子である。Nはタップ数(Tap

Count)で4から380まで設計可能。 N次FIR フィルタの数学的モデル。"D"はD型フリップフロップで単位遅延素子である。Nはタップ数(Tap

Count)で4から380まで設計可能。

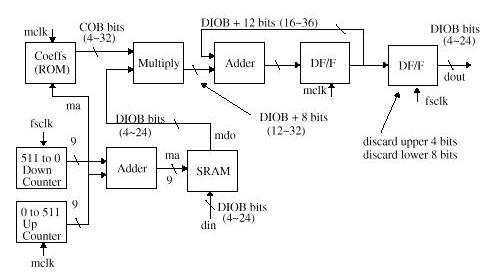

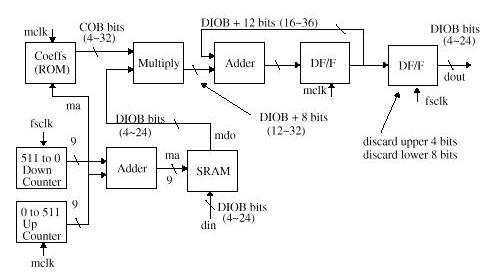

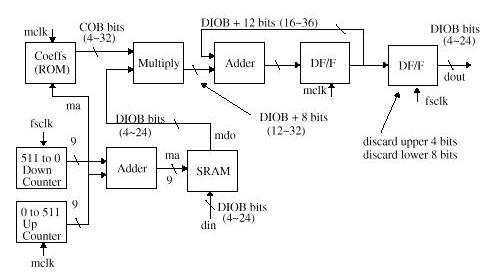

生成されるVHDLコードのブロック図。入力データはDIOBビット(4〜24)、係数はCOBビット(4〜32)である。入力データはRAMに書き込まれ、読み出される。係数はROMから読み出される。乗算器はDIOBビットxCOBビットで、その出力を累積し、最終的にDIOBビットデータとして出力する。注意:SRAMはハードマクロセルまたは外付けが好ましい。シンセシスすると巨大になります。 生成されるVHDLコードのブロック図。入力データはDIOBビット(4〜24)、係数はCOBビット(4〜32)である。入力データはRAMに書き込まれ、読み出される。係数はROMから読み出される。乗算器はDIOBビットxCOBビットで、その出力を累積し、最終的にDIOBビットデータとして出力する。注意:SRAMはハードマクロセルまたは外付けが好ましい。シンセシスすると巨大になります。

戻る 戻る

|