IIRフィルタのVHDLコードについて IIRフィルタのVHDLコードについて

2次 IIR フィルタの数学的モデル。これを最大8個までシリアル接続する。実際の回路では、b1、b2の極性が反転されていることに気を付けよう。 2次 IIR フィルタの数学的モデル。これを最大8個までシリアル接続する。実際の回路では、b1、b2の極性が反転されていることに気を付けよう。

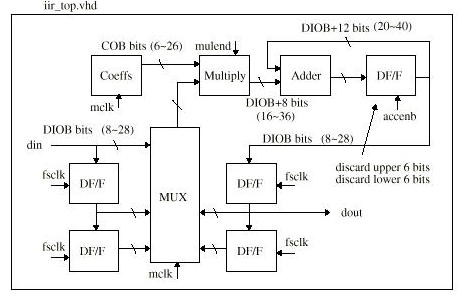

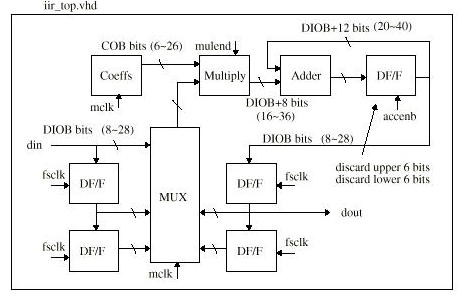

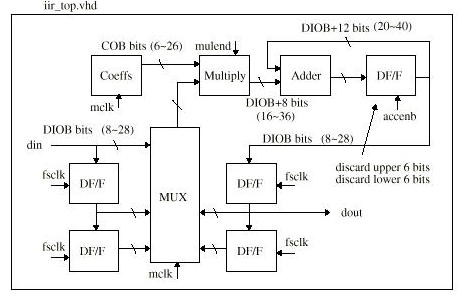

生成されるVHDLコードのブロック図。入力はDIOBビット(8〜28)、係数はCOBビット(6〜26)。上のモデルでは乗算器が5つあるが、ゲート数節約のため、DIOBxCOBビットの乗算器を時分割で使う。それゆえ、係数とデータをマルチプレクスする必要がある。乗算後のデータを累積し、DIOBビットとして出力する。 生成されるVHDLコードのブロック図。入力はDIOBビット(8〜28)、係数はCOBビット(6〜26)。上のモデルでは乗算器が5つあるが、ゲート数節約のため、DIOBxCOBビットの乗算器を時分割で使う。それゆえ、係数とデータをマルチプレクスする必要がある。乗算後のデータを累積し、DIOBビットとして出力する。

デジタルフィルタアナライザで"係数ビット長=8"とした場合COBは10となります。2ビット余裕を持たせた理由は、時折係数が1.0(実数)を超えるからです。またソフト上で"データビット長=8"とした場合DIOBは12ビットとなります。その理由は複数のIIRをシリアルにつなぐ場合、時折データが1.0を大きく超えるからです。 デジタルフィルタアナライザで"係数ビット長=8"とした場合COBは10となります。2ビット余裕を持たせた理由は、時折係数が1.0(実数)を超えるからです。またソフト上で"データビット長=8"とした場合DIOBは12ビットとなります。その理由は複数のIIRをシリアルにつなぐ場合、時折データが1.0を大きく超えるからです。

戻る 戻る

|