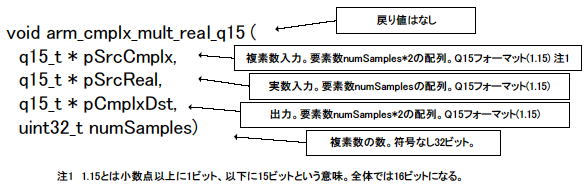

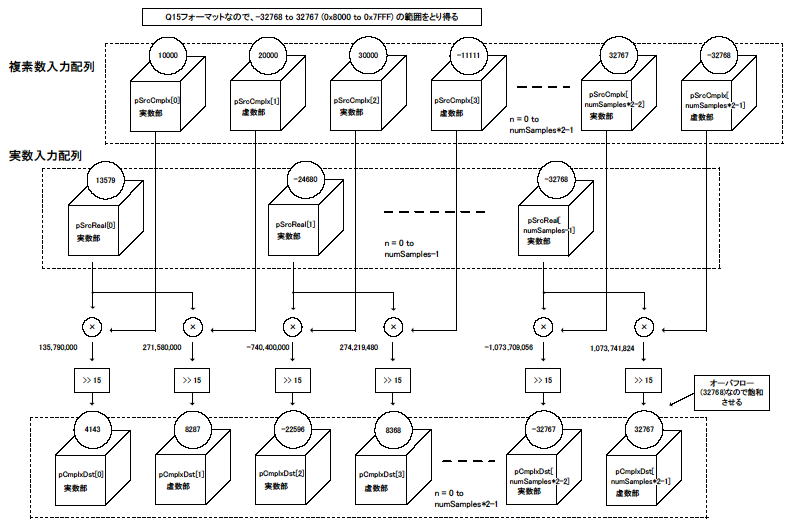

CMSIS_2_00\CMSIS\DSP_Lib\Source\Cortex-M4-M3\BasicMathFunctions\arm_cmplx_mult_real_q15.c IARprojects\src\projects\arm_cmplx_multr   乗算後は32ビットになる。その後15ビット右シフトして16ビットに収める。

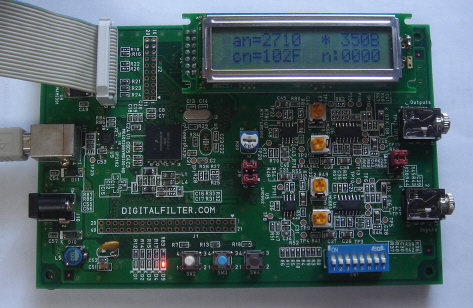

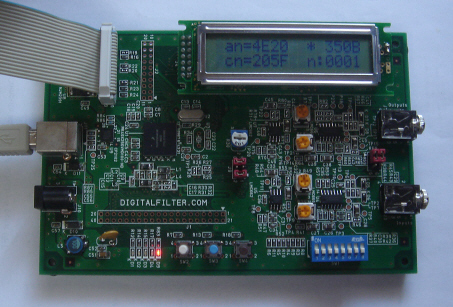

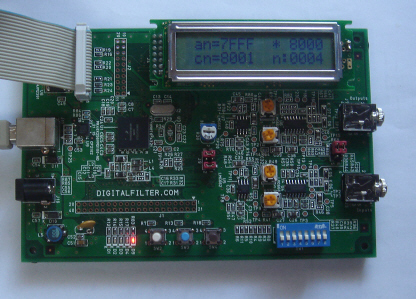

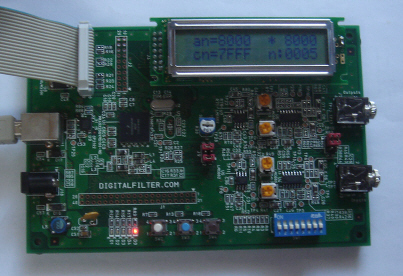

配列a, cの要素数はそれぞれ6、複素数の数は3。 配列bの要素数、実数の数は3。 上記のサンプルソースをDFFSKN40基板(デジタルフィルター社)にて実験した。Cortex-M4マイコンはPK40X256VMD100(Kinetis, フリースケール社)搭載。演算結果をLCDに16進数で表示している。 下の写真は最初の複素乗算の実数部。 a[0] = 10000 -> 0x2710 (実数部) b[0] = 13579 -> 0x350B c[0] = (a[0] b[0] >> 15) = 4143 = 0x102F  下の写真は最初の複素乗算の虚数部。 a[1] = 20000 -> 0x4E20 (虚数部) b[0] = 13579 -> 0x350B c[1] = (a[1] b[0] >> 15) = 8287 = 0x205F  下の写真は最後の複素乗算の実数部。 a[4] = 32767 -> 0x7FFF (実数部) b[2] = -32768 -> 0x8000 c[4] = (a[4] b[2] >> 15) = -32767 = 0x8001  下の写真は最後の複素乗算の虚数部。 a[5] = -32768 -> 0x8000 (虚数部) b[2] = -32768 -> 0x8000 c[5] = (a[5] b[2] >> 15) = 32768 <-- 16ビットの範囲を超えている ゆえにc[5] = 0x7FFF  複素数と実数の乗算。 乗算後に15ビット右シフトして16ビットに収めている。Q1.15フォーマットになる。 極値どうしの乗算に注意。(-32768)*(-32768)のときだけオーバーフローする。 |

Top Page