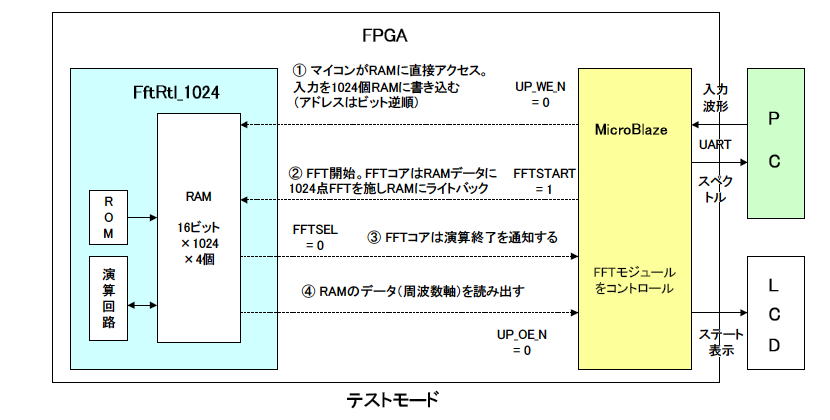

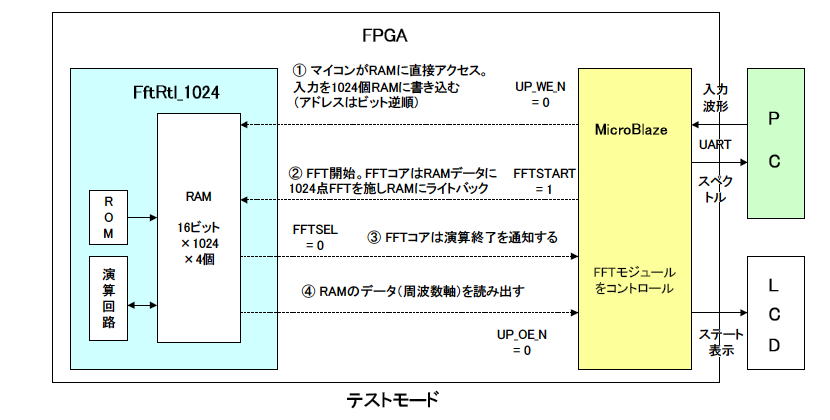

Between PC and FFT, MicroBlaze(MB) exists and controls UART and LCD. The

following shows the signal flow of "test mode". (1) MB send data

from PC to FFT's RAM -> (2) FFT starts calculation -> (3) FFT ends

it and notify to MB -> (4) MB sends data from FFT's RAM to PC. Finally

PC checks if the FFT result is correct or not. Between PC and FFT, MicroBlaze(MB) exists and controls UART and LCD. The

following shows the signal flow of "test mode". (1) MB send data

from PC to FFT's RAM -> (2) FFT starts calculation -> (3) FFT ends

it and notify to MB -> (4) MB sends data from FFT's RAM to PC. Finally

PC checks if the FFT result is correct or not.

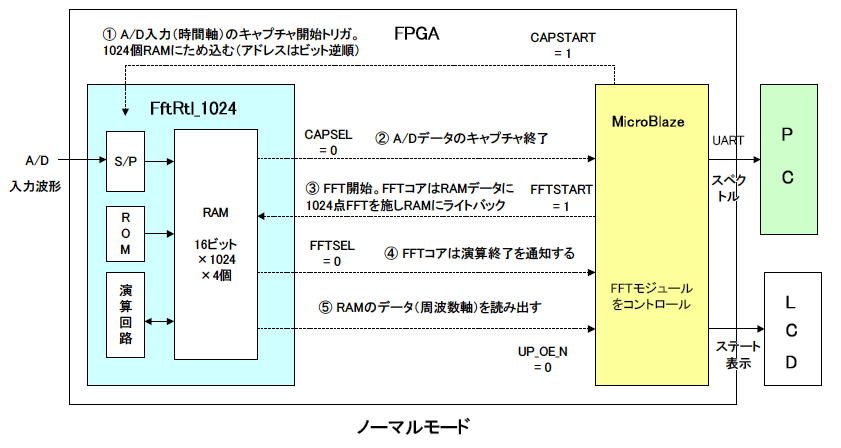

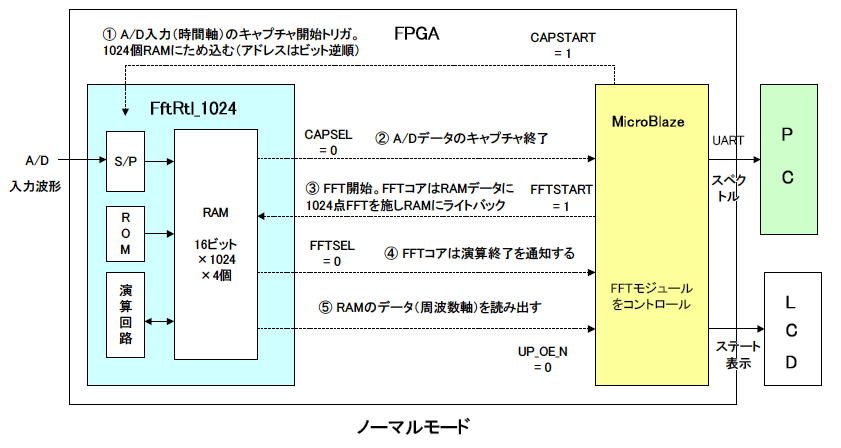

The following is "normal mode". (1) A/D converter injects data

to FFT -> (2) FFT starts calculation -> (3) FFT ends it and notify

to MB -> (4) MB sends data from FFT's RAM to PC. Finally PC shows the

spectrum in a graph. The following is "normal mode". (1) A/D converter injects data

to FFT -> (2) FFT starts calculation -> (3) FFT ends it and notify

to MB -> (4) MB sends data from FFT's RAM to PC. Finally PC shows the

spectrum in a graph.

That's it for this class. I show you a summary of "C2VHDL" That's it for this class. I show you a summary of "C2VHDL"

(1) Execute FFT in C language with floating point. <-- This is the start

point.

(2) Switch variables to fixed point in C. <-- Compare this result with

(1)'s result

(3) Describe it in VHDL and do RTL simulation. <-- Compare this result

with (2)'s result

(4) Run it in FPGA and send the result to PC. <-- Compare this result

with (3)'s result

In order to design hardware of FFT or other DSP stuff, the steps above

is a good way to achieve it. Finally, let me tell you the merit of C2VHDL. In order to design hardware of FFT or other DSP stuff, the steps above

is a good way to achieve it. Finally, let me tell you the merit of C2VHDL.

(1) For FFT, VHDL can be ten times faster than C.

(2) For couple FIR filters, VHDL can run them in parallel, that means twice

faster than C.

See you again!! Let me know your impression --> info@digitalfilter.com See you again!! Let me know your impression --> info@digitalfilter.com

|