5‐04 スループットを決める(続き)

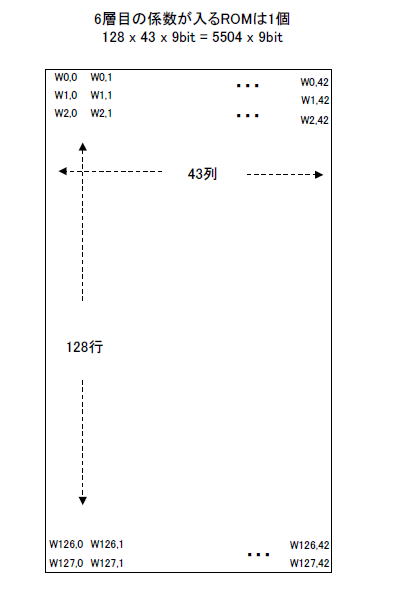

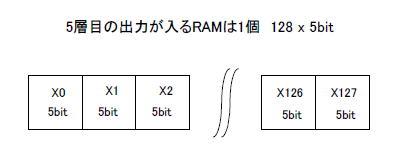

●6層目の入力データRAM

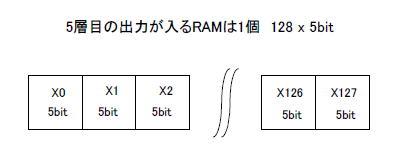

5層目の出力は128個あり、それぞれ5ビットなので、図5‐39のようにビット幅が5bit、アドレスが0〜127のRAMに格納されます。 |

図5-39 5層目の出力は128個、5bit

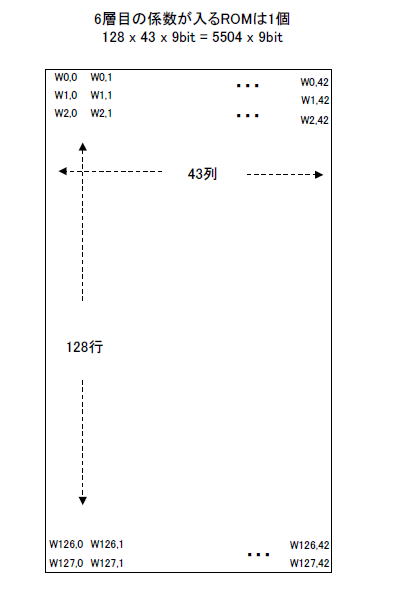

●6層目の重み係数ROM

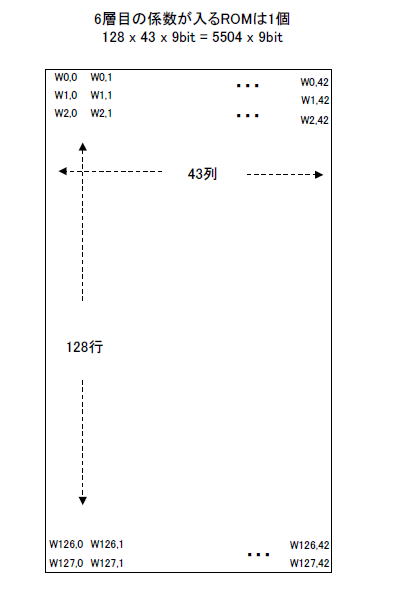

6層目の重み係数は図5‐40のようなROMに入ります。128個の入力にこのような128×43の行列を乗算し、43個の出力を得ます。係数の数は少ないですが、これらは‐256〜+255の値をとります(符号付き9ビット)。 |

図5‐40 128行×43列

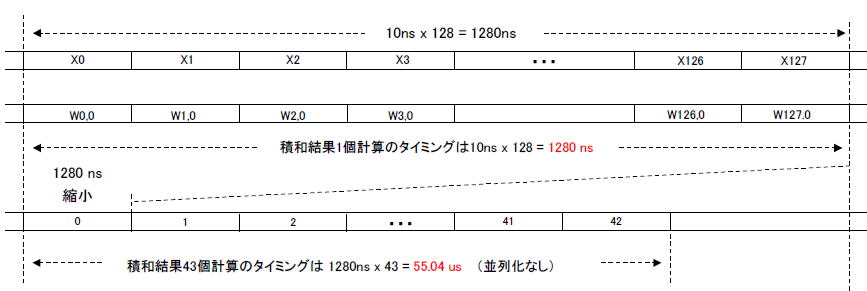

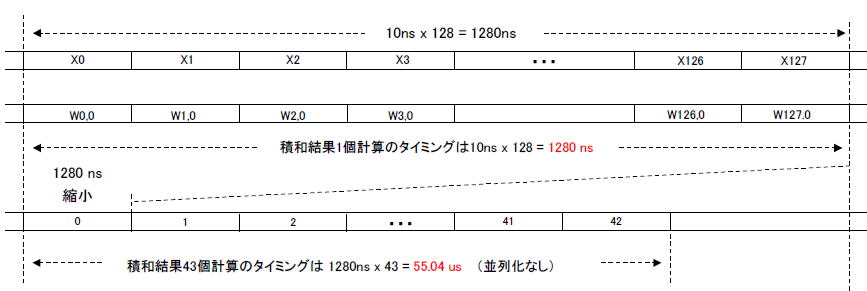

●128回の積和で出力1個が得られる

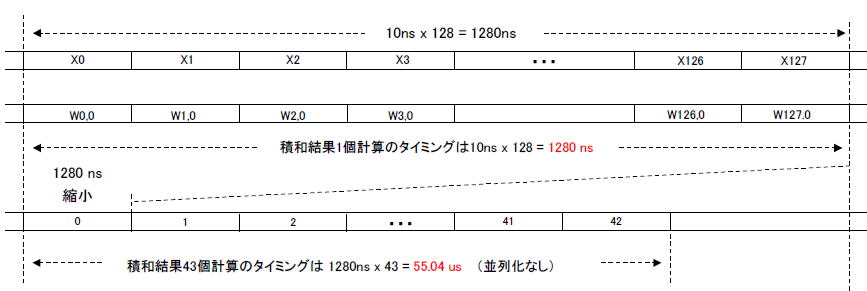

図5‐41にタイムチャートを示します。一番上は入力データRAM、2段目は重み行列ROMの読出しで、これらを乗算して累積します。128個累積したところで積和演算は終了し、出力データが一つ得られます。クロック100MHzとすると、10ns

x 128 = 1280nsになります。 |

図5‐41 積和演算のタイムチャート

●並列化しなくても間に合う

6層目の出力は43個あるので全部計算するのに1280ns x 43 = 55.04usとなります。スループット(320us)よりはるかに小さいため、並列化する必要はありません。ただし係数が9ビットなので、ここはビットシフト型ではなく、普通の乗算器を1個使います。

●各層ごとに320us未満であることを確認した!

CNN1ブロックは320us毎に次から次へと入力されます。したがって各層はそのペースに間に合うように処理する必要がありますが、大事なのは各層パイプラインで並列動作しているということです。

つまり1〜6までの「全層トータル」で320usということではなく、「各層単体」で320us未満であればOKということです(表5‐01)。 |

表5-1 各層320us未満で1枚処理できる

|

1層目 |

2層目 |

3層目 |

4層目 |

5層目 |

6層目 |

| 形状 |

CNN |

全結合 |

| 1ラインにかかる時間[us] |

10.08 |

9.36 |

15.84 |

11.52 |

- |

- |

| 1枚にかかる時間[us] |

282.24 |

262.08 |

221.76 |

161.28 |

163.84 |

55.04 |

| 係数の数 |

432 |

4,608 |

18,432 |

73,728 |

262,144 |

5,504 |

| 乗算器の数 |

16 |

128 |

128 |

512 |

16 |

1 |

| 乗算器のタイプ |

通常 |

ビットシフト型 |

通常 |

最初のページへ

目次へ戻る

|