2-02丂夞楬恾偲僞僀儉丒僠儍乕僩

仭傑偢偼1憌栚偐傜

丂偙偺EXCEL昞偵偼W1, W2, W3偲廳傒峴楍偑3偮偁傝傑偡偑丄嵟弶偺W1偼夋憸僨乕僞X乮嵟弶偺僔乕僩偺x_in峴乯偲忔嶼偝傟傑偡丅

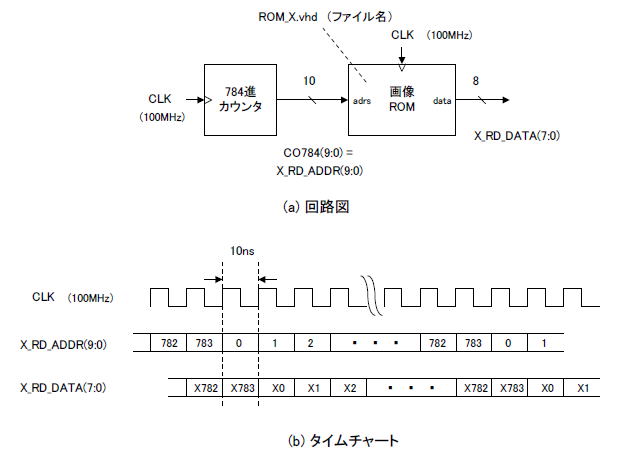

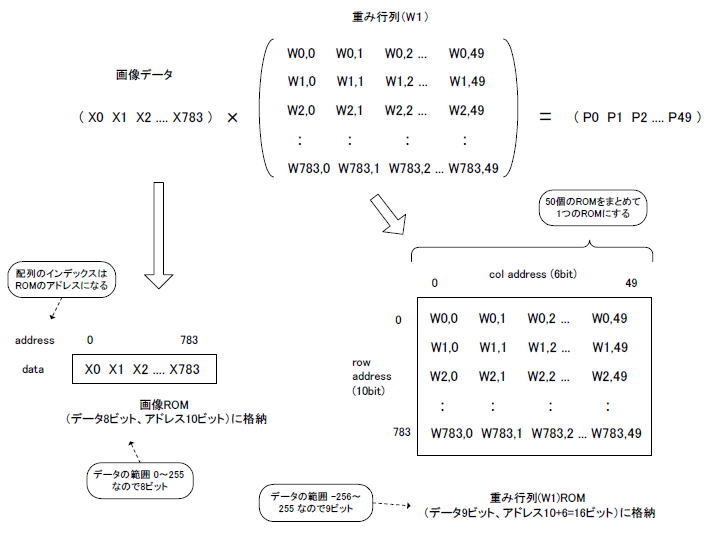

仠夋憸偺攝楍傪ROM偵妱傝摉偰傞

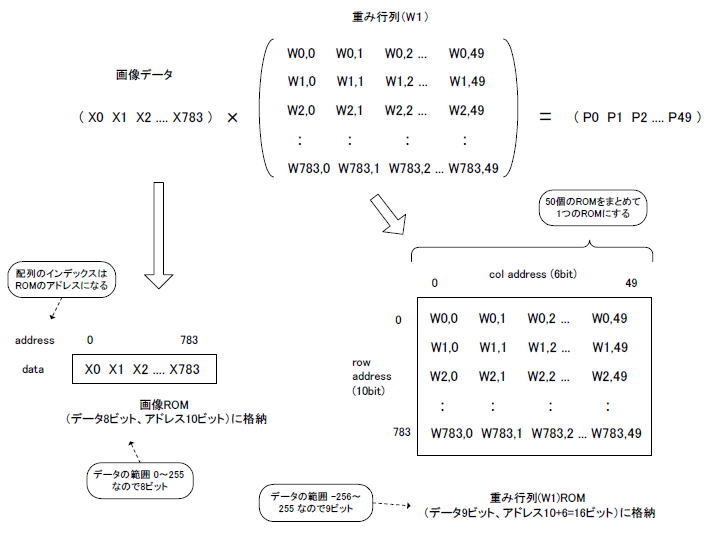

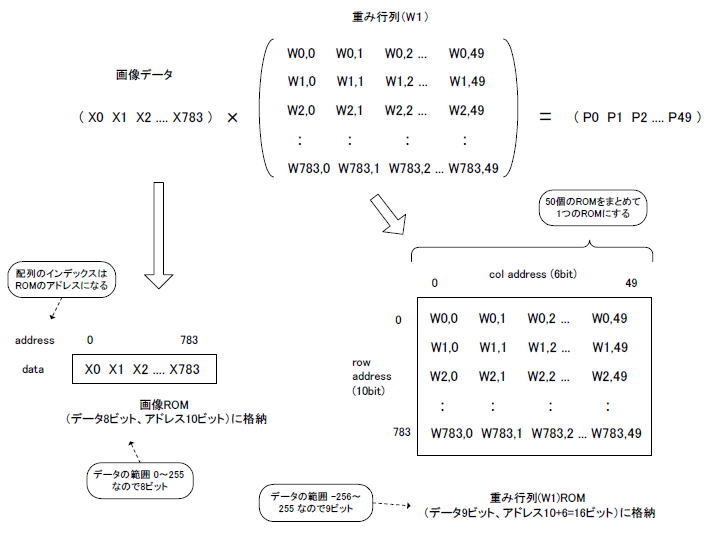

丂X偼梫慺悢784偺攝楍側偺偱丄恾2乚02偺傛偆偵儊儌儕乮ROM乯偵妱傝摉偰傑偡丅攝楍偺僀儞僨僢僋僗乮0乣783乯偑傾僪儗僗偵憡摉偡傞偺偱丄傾僪儗僗暆偼10價僢僩偵側傝傑偡丅傑偨僨乕僞偺斖埻偼0乣255側偺偱僨乕僞暆偼8價僢僩偵側傝傑偡丅

|

丂丂恾2乚02丂攝楍丄峴楍傪儊儌儕乮ROM乯偵妱傝摉偰傞

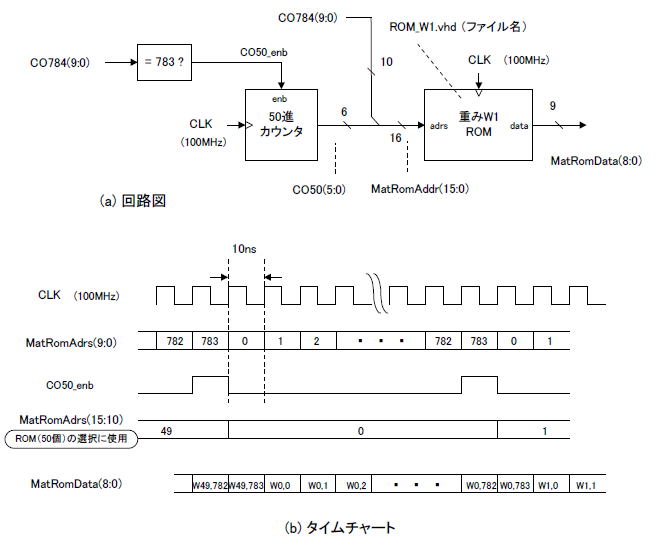

仠暋悢偺ROM偱廳傒偺峴楍傪峔惉偡傞

丂W1偼梫慺悢784亊50偺峴楍偱偁傝丄恾2乚02偺傛偆偵50屄偺ROM偵妱傝摉偰傑偡丅廲偺楍偑偦傟偧傟傾僪儗僗暆10價僢僩偺ROM偵側傝傑偡丅偦傟傪50屄傑偲傔忋偘偰1屄偺ROM偵偡傞偺偱丄慡懱偺傾僪儗僗暆偼10亄6亖16價僢僩偵側傝傑偡丅

丂傑偨僨乕僞偺斖埻偼-256乣255側偺偱僨乕僞暆偼9價僢僩偵側傝傑偡丅2偺曗悢偱昞尰偡傞偺偱嵟忋埵偼晞崋價僢僩偱偡丅

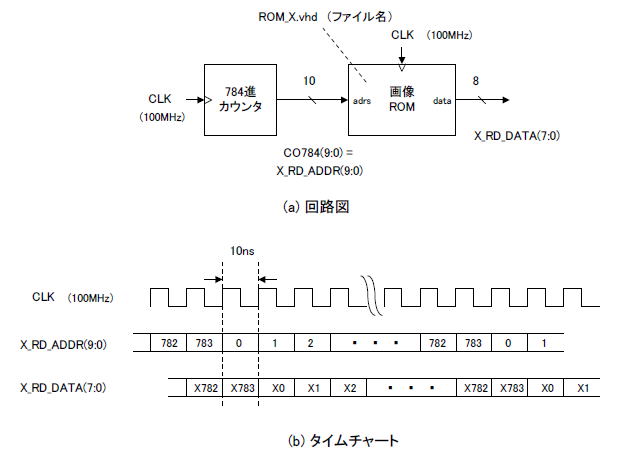

仠夋憸ROM偺傾僪儗僗傪僇僂儞僞偱惗惉

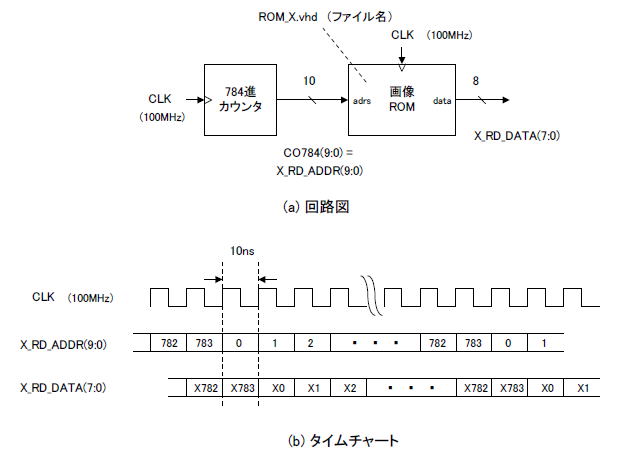

丂攝楍偺僀儞僨僢僋僗偼ROM偺傾僪儗僗偵憡摉偟丄恾2乚03(a)偺傛偆偵乽784恑僇僂儞僞乿偱惗惉偟傑偡丅

丂摨恾(b)偼偦偺僞僀儉僠儍乕僩偱丄X_RD_ADDR偼CLK(100MHz,)傪0乣783傑偱僇僂儞僩傾僢僾偟丄偦偺屻0偵栠偭偰摨偠傛偆偵孞傝曉偟傑偡丅

丂X_RD_DATA偼ROM偐傜撉傒弌偝傟傞僨乕僞偱丄摨恾(b)偺傛偆偵CLK偺1僒僀僋儖(10ns)抶墑偟偰X0乣X783偑弌椡偝傟傑偡乮僋儘僢僋摨婜宆ROM)丅 |

丂丂恾2乚03丂夋憸ROM偺傾僪儗僗偲僨乕僞偺撉傒弌偟

仠廳傒峴楍ROM偺傾僪儗僗惗惉

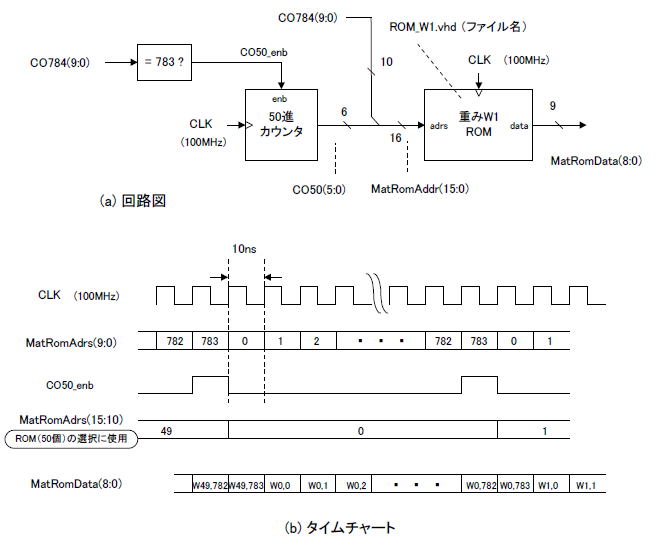

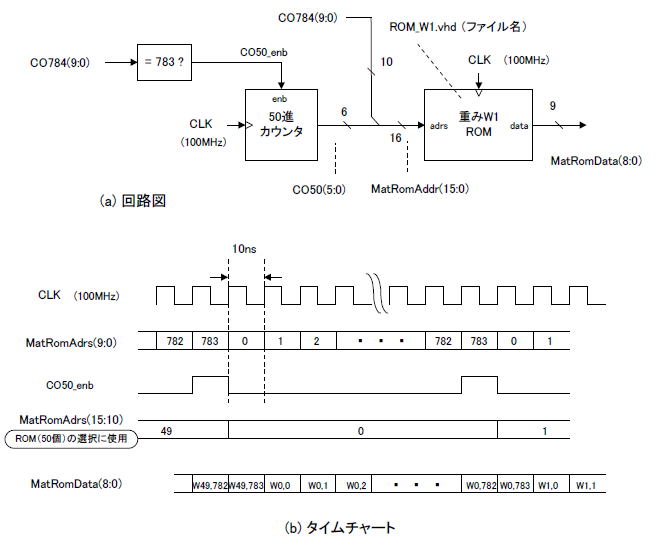

丂恾2乚04偵峴楍W1偺ROM偺傾僪儗僗惗惉朄傪帵偟傑偡丅恾2乚03(a)偱惗惉偟偨784恑僇僂儞僞(CO784)傪壓埵10價僢僩偲偟傑偡丅

丂偝傜偵50恑僇僂儞僞傪愝偗傑偡丅偦傟偼784恑僇僂儞僞偑嵟戝抣(783)偵側偭偨帪偩偗僇僂儞僩傾僢僾偟丄偦傟(CO50)偑忋埵6價僢僩偵側傝傑偡丅

丂摨恾(b)偵偦偺僞僀儉僠儍乕僩傪帵偟傑偡丅MatRomAddr偺壓埵10價僢僩偑0乣783傑偱僇僂儞僩傾僢僾偝傟傞娫丄忋埵6價僢僩偼侽傪曐偪傑偡丅

丂偦偺屻忋埵6價僢僩偼侾偲側傝丄壓埵10價僢僩偼嵞傃0乣783傑偱僇僂儞僩傾僢僾偟傑偡丅

丂廳傒W1ROM乮僼傽僀儖柤ROM_W1.vhd)偺拞偵偼梫慺悢784屄偺ROM偑50屄偁傝丄MatRomAddr偺忋埵6價僢僩偼偦偺ROM偺慖戰偵巊梡偝傟傑偡丅 |

丂丂恾2乚04丂廳傒ROM偺傾僪儗僗偲僨乕僞偺撉傒弌偟

師偺儁乕僕傊

栚師傊栠傞

|