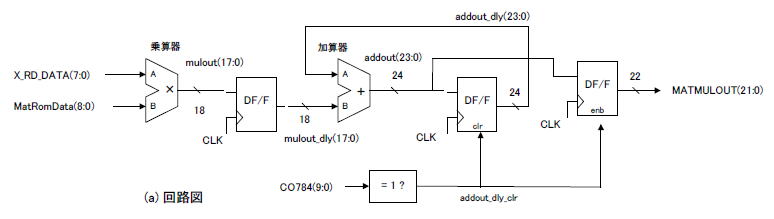

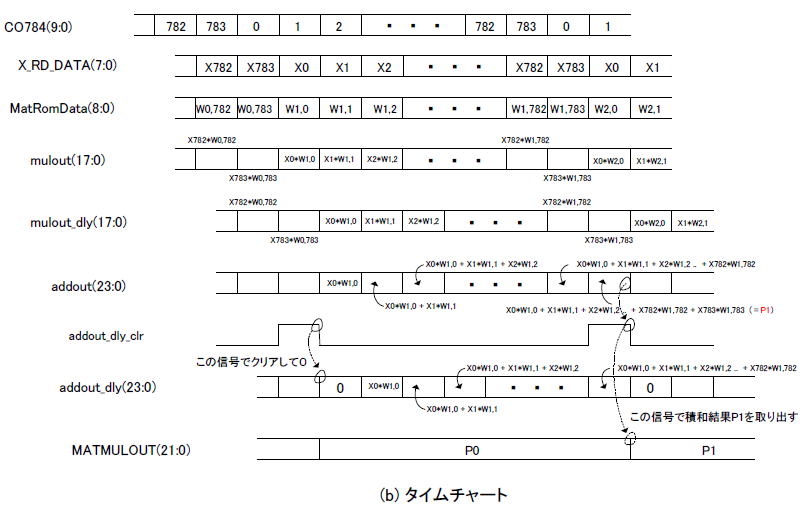

丂丂恾2乚05丂784梫慺傪愊榓墘嶼偡傞丅寢壥偼50屄偵側傞

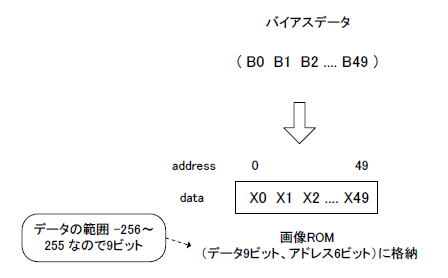

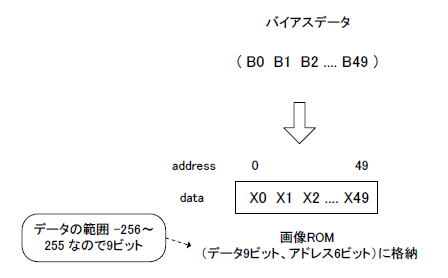

丂丂恾2乚06丂僶僀傾僗偺梫慺悢偼50丅偙傟傕ROM偵奿擺偡傞

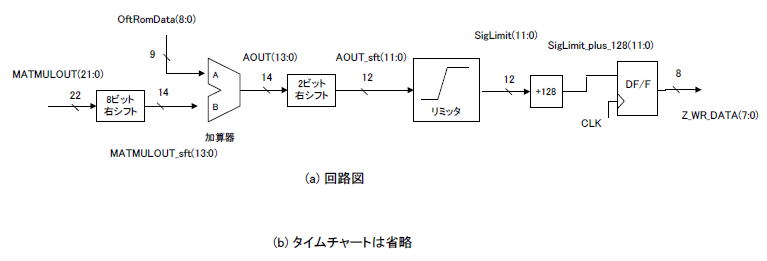

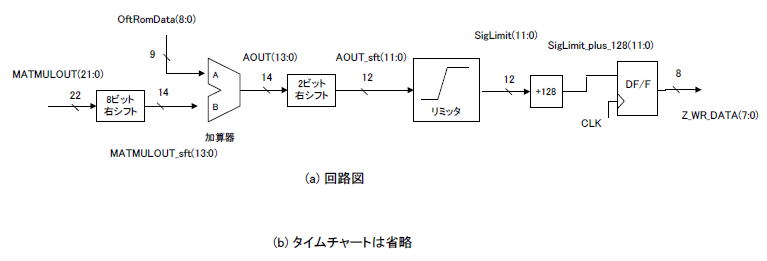

丂丂恾2乚07丂僶僀傾僗傪懌偟偰媈帡僔僌儌僀僪娭悢偵偐偗傞

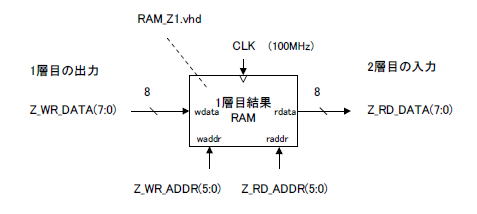

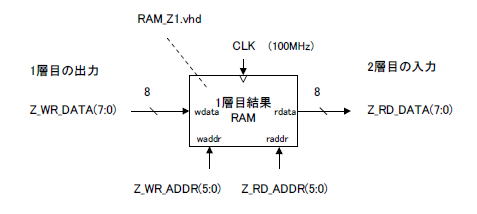

丂丂恾2乚08丂1憌栚偺寢壥傪2憌栚偵搉偡RAM 師偺儁乕僕傊 栚師傊栠傞 |

|||||||

丂丂恾2乚05丂784梫慺傪愊榓墘嶼偡傞丅寢壥偼50屄偵側傞

丂丂恾2乚06丂僶僀傾僗偺梫慺悢偼50丅偙傟傕ROM偵奿擺偡傞

丂丂恾2乚07丂僶僀傾僗傪懌偟偰媈帡僔僌儌僀僪娭悢偵偐偗傞

丂丂恾2乚08丂1憌栚偺寢壥傪2憌栚偵搉偡RAM 師偺儁乕僕傊 栚師傊栠傞 |

|||||||