■3層目

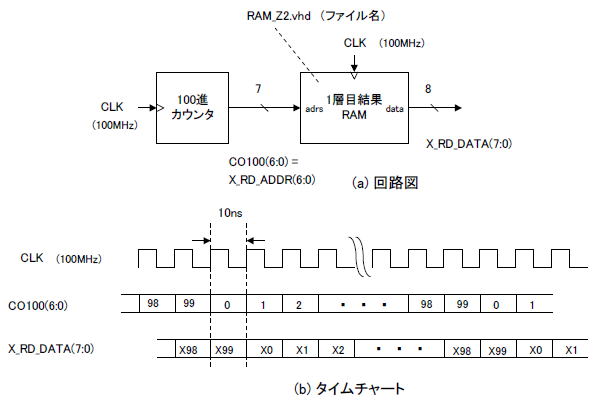

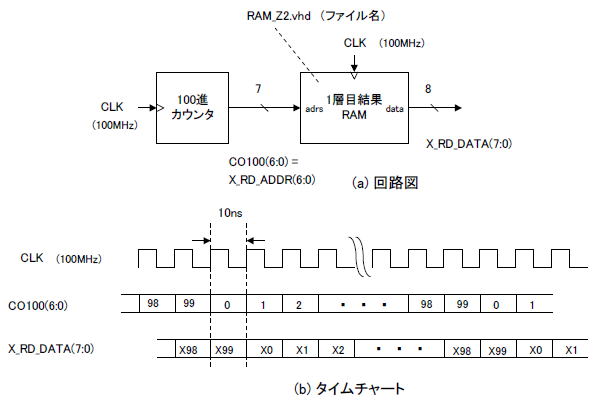

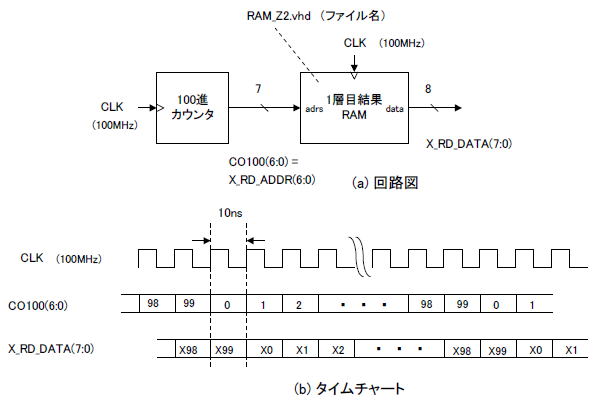

2層目の演算結果は図2‐12のようにRAM_Z2.vhdにあるのでそれを読み出します。アドレスは例によってカウンタで生成しますが、この場合は100進カウンタになります。

同図(b)のタイムチャートで分かるようにに2層目に入力されるデータはX0〜X99まで100個です。 |

図2‐12 2層目の結果が入ったRAMを読んで3層目に渡す部分

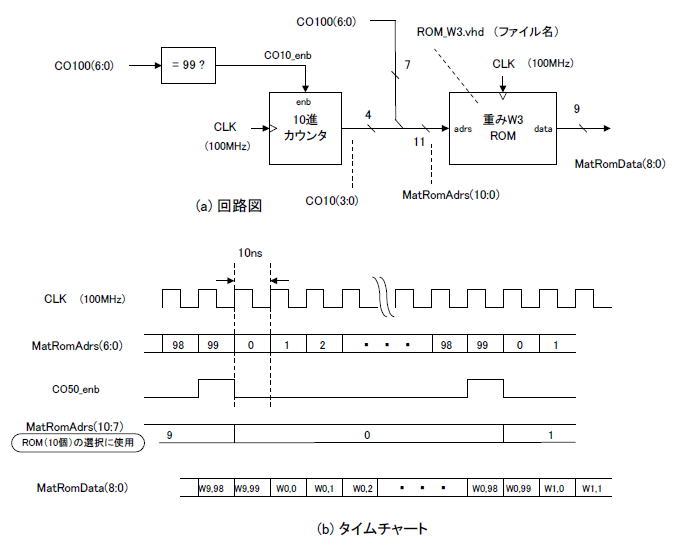

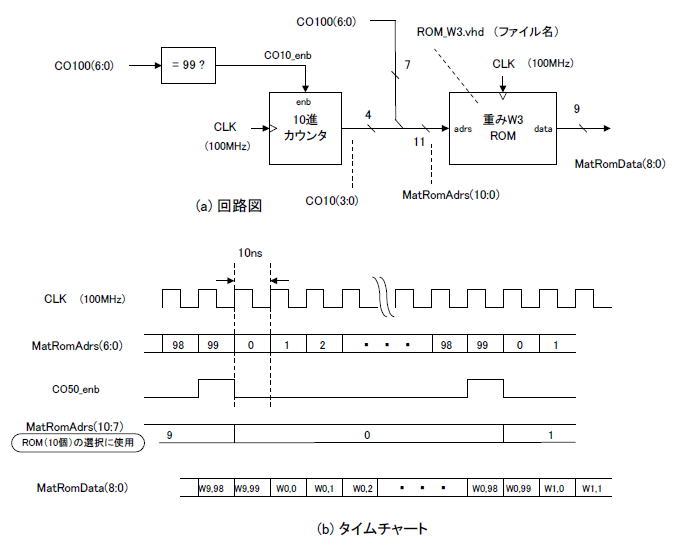

●重み行列ROMのアドレス生成

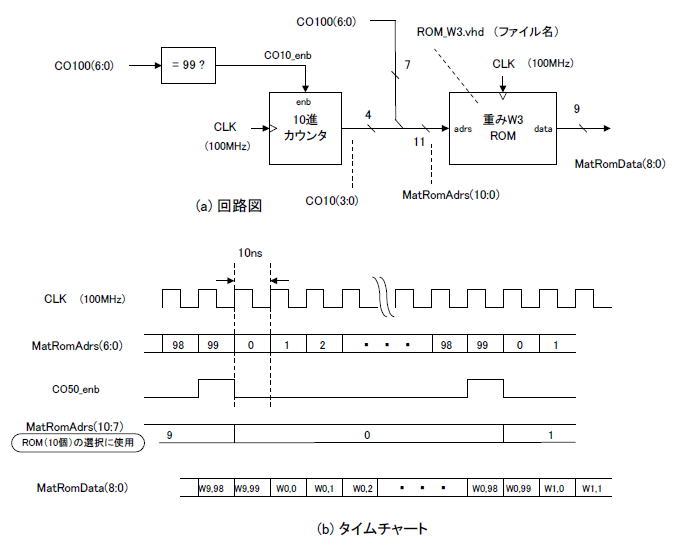

図2‐13に行列W3のROMのアドレス生成法を示します。図2‐12(a)で生成した100進カウンタ(CO100)を下位7ビットとします。

さらに10進カウンタを設けます。それは100進カウンタが最大値(99)になった時だけカウントアップし、それが上位4ビットになります。

図2‐13(b)にそのタイムチャートを示します。MatRomAddrの下位7ビットが0〜99までカウントアップされる間、上位4ビットは0を保ちます。

その後上位7ビットは1となり、下位7ビットは再び0〜99までカウントアップします。

重みW3ROM(ファイル名ROM_W3.vhd)の中には要素数100個のROMが10個あり、MatRomAddrの上位4ビットはそのROMの選択に使用されます。 |

図2‐13 重みのROMを読む部分

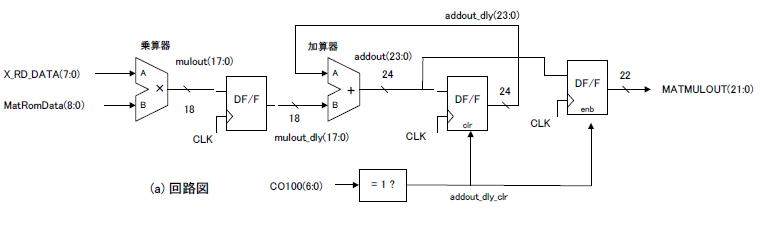

●積和演算の部分

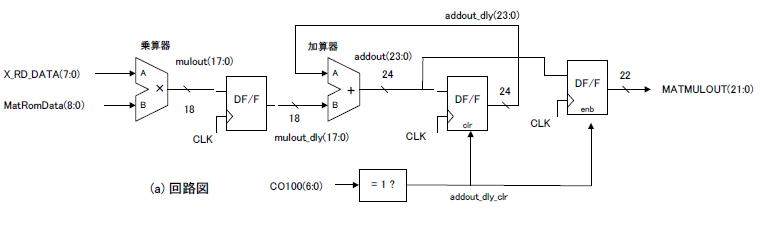

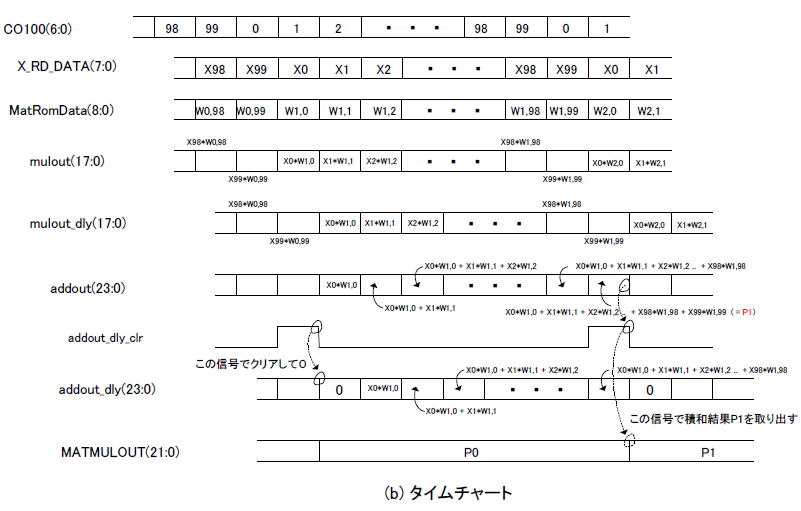

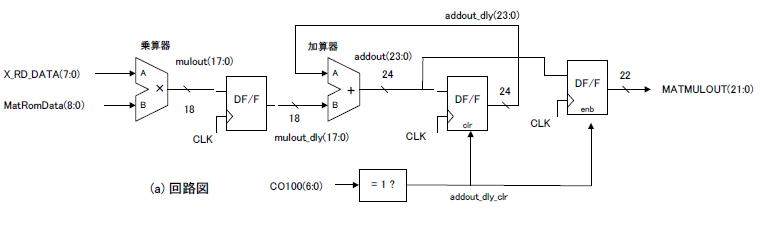

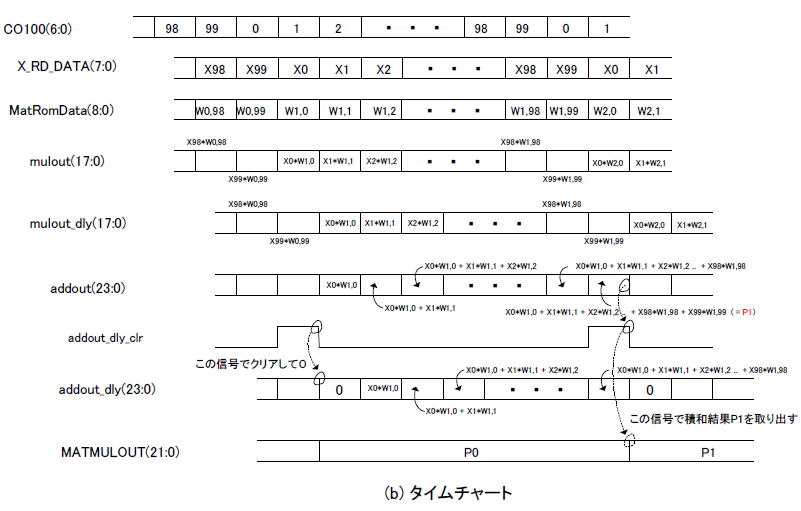

画像ROMからの出力X_RD_DATAと、重みROMからの出力MatRomDataは図2‐14(a)に示すように乗算器に入力されます。

その後、加算器と遅延器によって累積され、積和演算結果が得られます。その仕組みは1層目と同じなので省略します。

同図(b)はタイムチャートです。加算結果addoutはCO100=1のタイミングでラッチされMATMULOUTとなります。これが行列乗算の最初の要素P0になります。P0,

P1, P2, ... , P9まで10個演算して終了します。 |

図2‐14 100要素を積和演算する。結果は10個になる

●バイアス加算で3層目終了

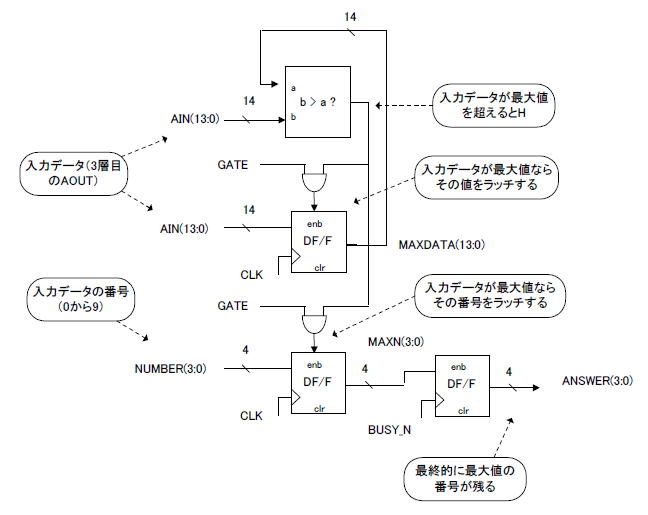

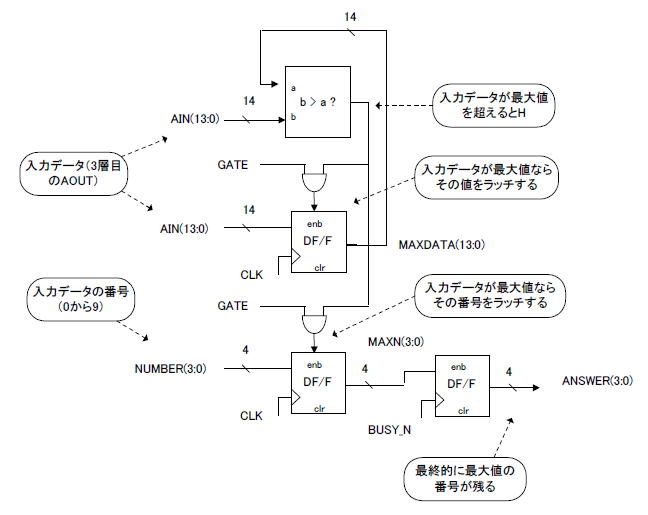

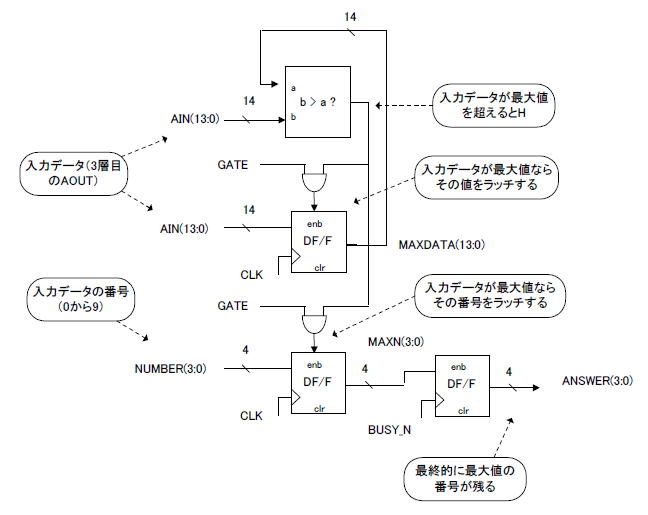

バイアス加算の仕組みは1層目と同じなので省略します。また最後の層はシグモイド関数は使用しません。バイアス加算後の値AOUTがこの層の出力になり、それは図2‐15のような判定回路(judge.vhd)に入力されます。

判定回路のタイムチャートは省略します(後々シミュレーションで確認)。

判定回路の出力ANSWERは推論結果になります。テスト画像データの1枚目なら「7」になるはずです。 |

図2‐15 3層目の出力から数値を判定するjudge.vhd

最初のページへ

目次へ戻る

|