仠1憌栚偺寢壥傪RAM偵棴傔崬傓晹暘

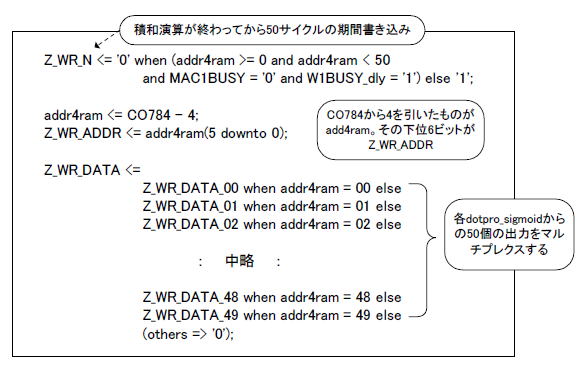

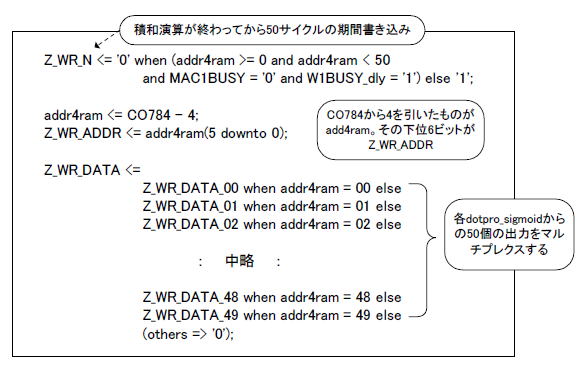

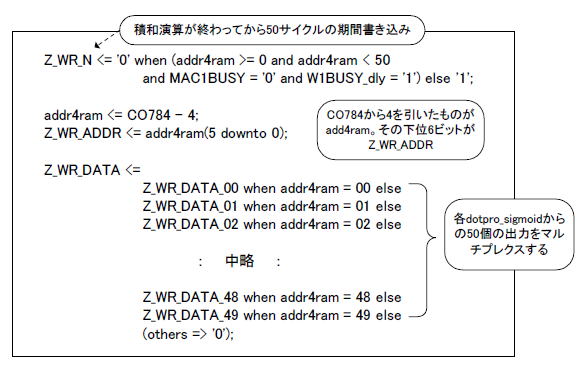

丂1憌栚偺廳傒峴楍偼784亊50側偺偱忔嶼寢壥偼50屄偱偡丅偦傟傜偼暲楍偵摨帪偵寁嶼偝傟傑偡偑丄僶僀傾僗傪壛嶼偡傞僾儘僙僗偵傛傝丄1僒僀僋儖枅偢傟側偑傜弌椡偝傟傑偡(恾3-04偺僔僌儌僀僪寢壥Z0,

Z1, ... Z49)丅偦傟傜偼儅儖僠僾儗僋僒偱懡廳壔偝傟傑偡乮Z_WR_DATA丄壓偐傜3抜栚乯丅

丂戞2復偲摨條偵丄1憌栚偺寢壥(Z0, Z1, ... Z49)傪偄偭偨傫RAM偵棴傔崬傒傑偡丅恾3-04偺傛偆偵RAM偺彂偒崬傒傾僪儗僗Z_WR_ADDR偲丄彂偒崬傒僀僱乕僽儖Z_WR_N傪惗惉偟傑偡丅 |

丂丂恾3-04丂1憌栚偺寢壥傪RAM偵彂偄偰2憌栚偑撉傓

丂恾3-04偺僞僀儉僠儍乕僩傪婎偵VHDL壔偡傞偲儕僗僩3-03偺傛偆偵側傝傑偡丅addr4ram偼CO784偐傜4傪堷偄偨傕偺偱丄偦偺壓埵6價僢僩偑Z_WR_ADDR偵側傝傑偡丅

丂add4ram偑0乣49偺婜娫傪BUSY怣崋偱儅僗僋偟偰Z_WR_N偵側傝傑偡丅 |

丂丂儕僗僩3-03丂RAM_Z1偵擖椡偡傞怣崋

仠丂奺庬BUSY怣崋偺愢柧

丂1憌栚layer1.vhd撪偵偼偄偔偮偐BUSY怣崋偑偁傞偺偱恾3-05偱愢柧偟傑偡丅儕僙僢僩怣崋RST_N偼嵟弶偺5us偺婜娫L乮傾僋僥傿僽乯偵側傝傑偡丅偦傟偑H偵側傞偲墘嶼偑僗僞乕僩偟傑偡丅

丂廳傒峴楍偼784亊50丄偙傟傪50暲楍偱張棟偡傞偺偱丄愊榓墘嶼偼784僒僀僋儖偱廔椆偟傑偡丅偙傟偼MAC1BUSY偑H偺婜娫偱偡丅

丂偦偺屻丄僶僀傾僗壛嶼丄僔僌儌僀僪偱1憌栚偺寢壥傪摼側偑傜RAM偵彂偒崬傒傑偡丅偙傟偼RAM1BUSY偑H偺婜娫偱偡丅

丂MAC1BUSY偲RAM1BUSY偺榑棟榓偑W1BUSY偵側傝傑偡丅偦偺斀揮偑BUSY_N偱偙傟偑L乮傾僋僥傿僽乯偺婜娫偼2憌栚偼懸婡忬懺偱丄H偵側傞偲2憌栚偺墘嶼偑僗僞乕僩偟傑偡丅 |

丂丂恾3-05丂BUSY怣崋偲僒僀僋儖悢

丂摨恾偺傛偆偵1憌栚偺墘嶼偵偵偐偐傞帪娫偼840僒僀僋儖庛偵側傝傑偡丅僔儈儏儗乕僔儑儞偱寁應偡傞偺偱乽師偺儁乕僕傊乿傪僋儕僢僋偟傑偟傚偆丅

|

師偺儁乕僕傊

栚師傊栠傞

|