仭弌椡夋憸偺彂偒崬傒

仠撉傒弌偟仺墘嶼仺彂偒崬傒

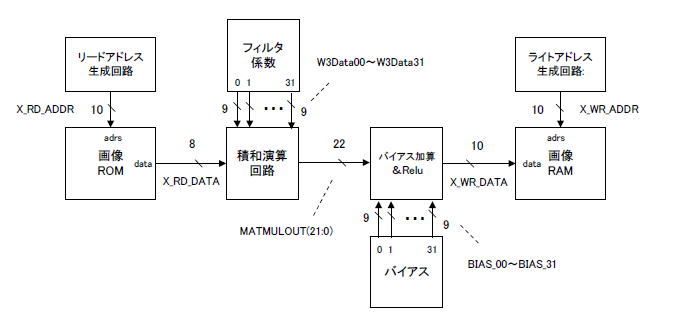

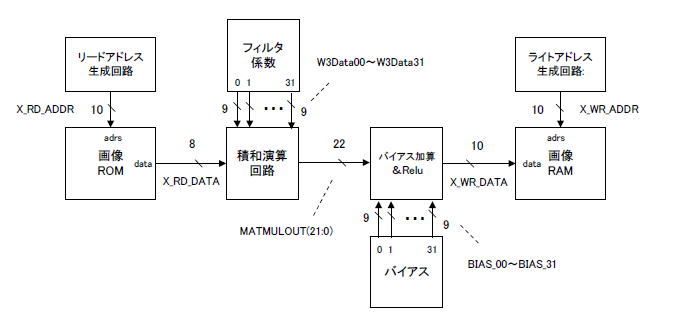

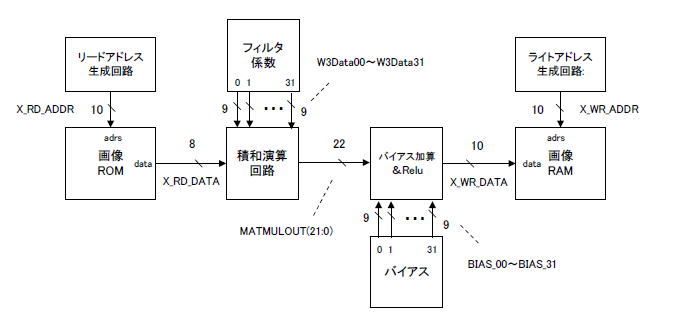

丂恾8-54偼3憌栚傪VHDL壔偟偨嵺偺僽儘僢僋恾偱偡丅乽夋憸ROM乿偵偼偁傜偐偠傔僷僨傿儞僌傪巤偝傟偨16亊16偺夋慺僨乕僞偑擖偭偰偄傑偡丅

丂偦偟偰夋憸ROM偺儕乕僪傾僪儗僗傪恾8-53偵側傜偭偰惗惉偡傟偽丄im2col娭悢偲摨偠弴斣偱夋慺偑弌偰偒傑偡丅偦偆偟偰摼傜傟偨夋慺僨乕僞偲廳傒學悢偲偺愊榓墘嶼乮忔嶼偼價僢僩僔僼僩偱乯傪峴偄傑偡丅

丂偦偺屻偼僶僀傾僗壛嶼仺Relu偲巤偟丄嵟屻偵墘嶼寢壥傪乽夋憸RAM乿偵彂偒崬傫偱忯傒崬傒3憌栚偼廔椆偱偡丅 |

丂丂恾8-54丂ROM偐傜撉傫偱墘嶼偟偰RAM偵彂偄偰廔傢傝

仠僷僨傿儞僌傪巤偟偨忬懺偱RAM偵彂偄偰偍偔偲師偺憌偱妝

丂X_WR_DATA偐傜偼14亊14偺夋慺抣偑弌偰偒傑偡偑丄偙傟傜傪僷僨傿儞僌傪巤偟偨忬懺偱夋憸RAM偵彂偒崬傫偱偍偔偲屻乆偺憌偱曋棙偵側傝傑偡丅

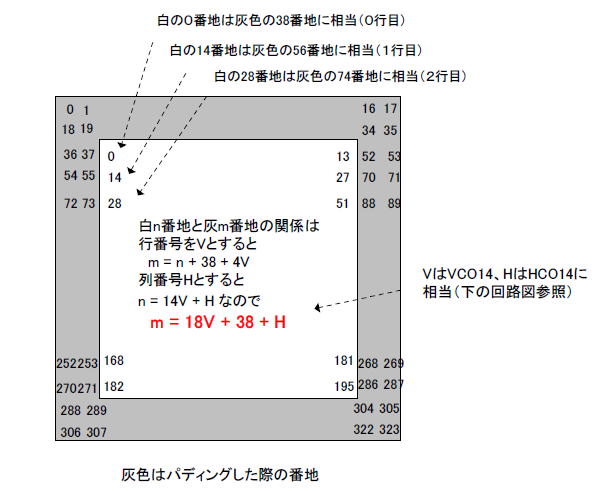

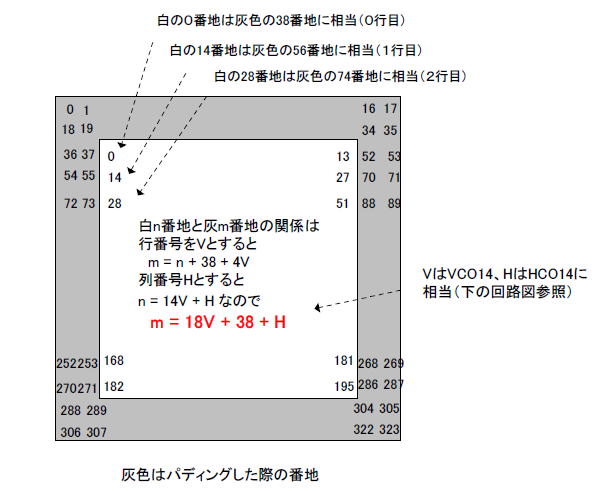

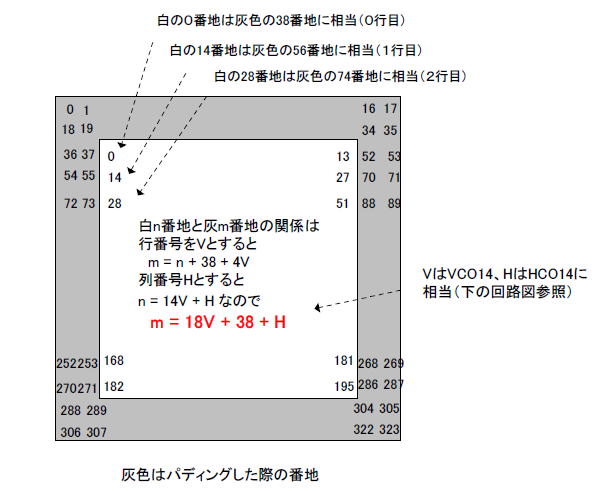

丂恾8-55偺敀偺晹暘偼14亊14偺夋憸丄奃怓偺榞偼偦傟偵僷僨傿儞僌傪巤偟偰18亊18偺夋憸偵偟偨傕偺偱偡丅弌椡僷僨傿儞僌偺暆偼俀偱偁傞偙偲偵拲堄偟傑偟傚偆丅

丂敀偺夋憸偵偼0乣195傑偱斣崋偑晅偗傜傟偰偄傑偡丅偙偺斣崋傪n斣抧偲屇傇偙偲偵偟傑偡丅

丂傑偨奃怓偺夋憸偵偼0乣323傑偱斣崋偑晅偗傜傟偰偍傝丄偙偺斣崋傪m斣抧偲屇傇偙偲偵偟傑偡丅 |

丂丂恾8-55丂弌椡偺僷僨傿儞僌偺暆偼2側偺偱18x18偵側傞

丂m偲n偺娭學偼摨恾偺傛偆偵丄m = 18V + 38 + H 偲側傝傑偡丅偙偙偱V偲偼廲曽岦14恑僇僂儞僞(VCO14)偺抣丄H偼墶曽岦14恑僇僂儞僞(HCO14)偺抣偱偡丅

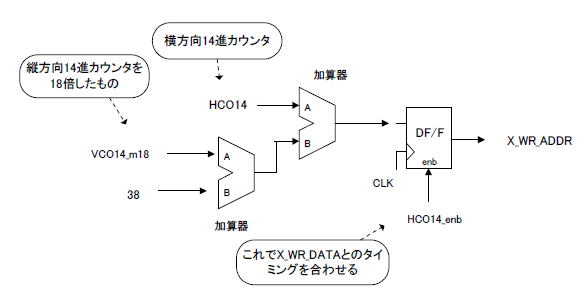

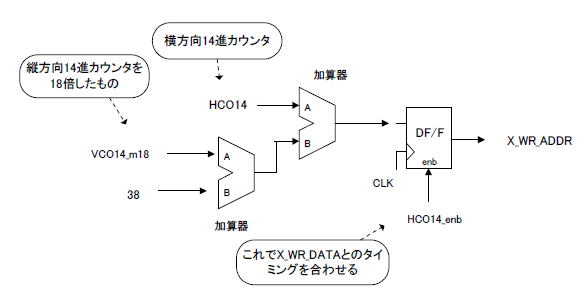

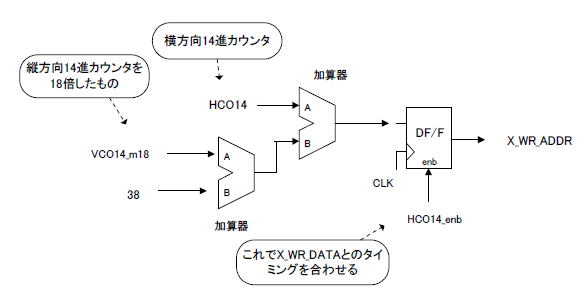

丂偟偨偑偭偰恾8-56偺傛偆側夞楬偱夋憸RAM偺彂偒崬傒傾僪儗僗傪惗惉偱偒傑偡丅 |

丂丂恾8-56丂彂偒崬傒傾僪儗僗惗惉夞楬

嵟弶偺儁乕僕傊

栚師傊栠傞 |