コラム141 Quartus、NiosII SBTで書き込んでSignalTapで見る手順

Quartus Primeは19.1 Lite Edition、OSはLinuxであることを前提にしています。バージョンやOSの違い等で動作しない場合はこれを参考にプロジェクトを一から構築してください。

またこの書籍にはQuartus, NiosII SBT, SignalTap, ModelSimの使い方に加え、画像処理回路の詳しい説明があるので参考にしてください。

●Quartusでハードウエアを書き込む

①このQuartusプロジェクトを解凍してホームディレクトリ\DE1-SoC\FPGAディレクトリに置く。

②QuartusからVideoProcプロジェクトを開いてStart Compilationボタンを押す。

③Compilationに成功したらProgrammerアイコンでプログラムする。

ロジック使用量はここにあるように69%、メモリ使用量は40%になりました。

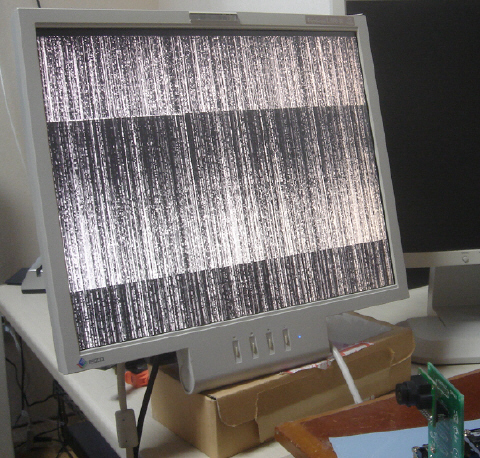

この時点ではまだNiosIIのソフトがない(カメラのレジスタが設定されていない)ので写真14-07のような画面になります。 |

写真14-07 カメラのレジスタ設定がないとこんなもの

●NiosII SBTでソフトウエアを書き込む

FPGA内部にNiosIIというソフトマクロマイコンがあり、そのソフトを書き込みます。ソフトはC言語で書かれており、カメラのレジスタ設定用です。マイコンは電源立ち上げ時に一度だけ動作します。

①QuartusのTools -> NiosII Software BuildTools for Eclipse(NiosII SBT)を選択する。

②VideoProcディレクトリを選択する。

③app00の上で右クリックし、NiosII -> BSP Editorを選択し、Generateボタンを押す。

④app00の上で右クリックし、Build Projectを選択する。

⑤app00の上で右クリックし、Run As -> NiosII Hardwareを選択。ソフトが書き込まれ自動的にスタートする。

するとカメラのレジスタが設定され、写真14-08のような画面になります(SW2のみHにした場合)。 |

写真14-08 カメラのレジスタ設定後。YUVのYのみ表示される。

●SignalTapでFPGA内部信号を確認

ここにあるようにSW0をHにすると「エミュレータモード」になり、カメラの代わりにMNIST画像を入力することができます。その際の演算がPythonと同じになっているか確認してみましょう。

①上記に倣ってQuartusでハードウエア、NiosII SBTでソフトウエアを書き込む。

②Tools -> Signal Tap Logic Analyzerを選択する。

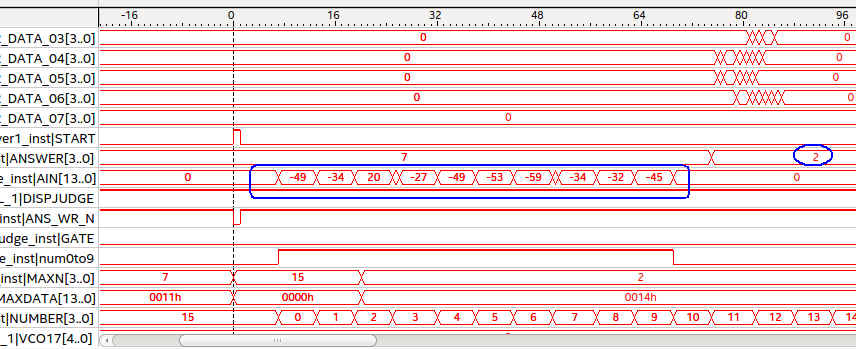

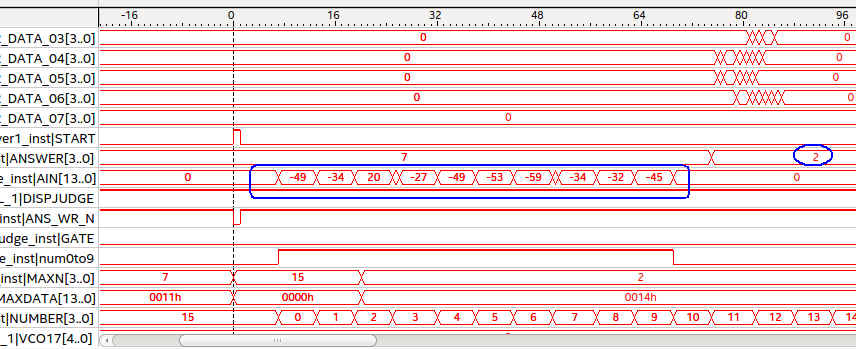

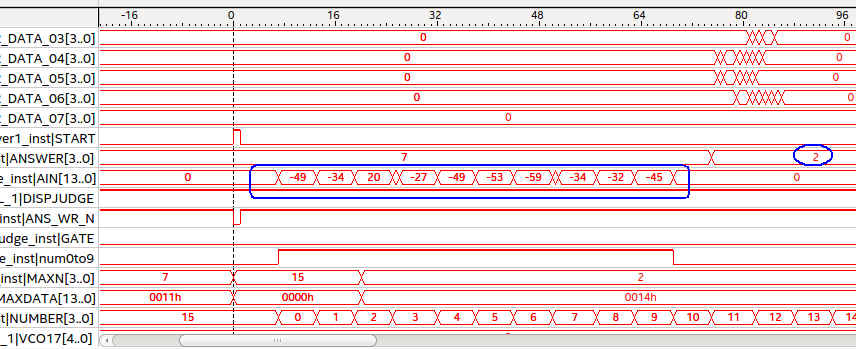

③Run Analysisボタンをクリックすると図14-05のような波形が現れる(SW0=H,

SW1=L, SW2=Lの場合)。

④観測する信号を変える場合はここを参考にしましょう。 |

図14-05 SignalTapでFPGA内部信号を見る

●Pythonと同じことがFPGA内部で起こっている

図14-06はPythonにおける演算結果です。2段目を見ると図14-05とピタリ一致しています。

エミュレータモードではMNISTテスト画像を入力します。ノーマルモードではそれがカメラ画像に切り替わるだけなので(ここ参照)、推論品質(MNIST対象で98.53%)は保たれます。 |

図14-06 Pythonの結果と比較(Anaconda Jupyter Labで動作)

目次へ戻る |