12-01丂ROM撪偺夋憸8枃偑FPGA偱惓偟偔悇榑偝傟偰偄傞偙偲傪妋擣

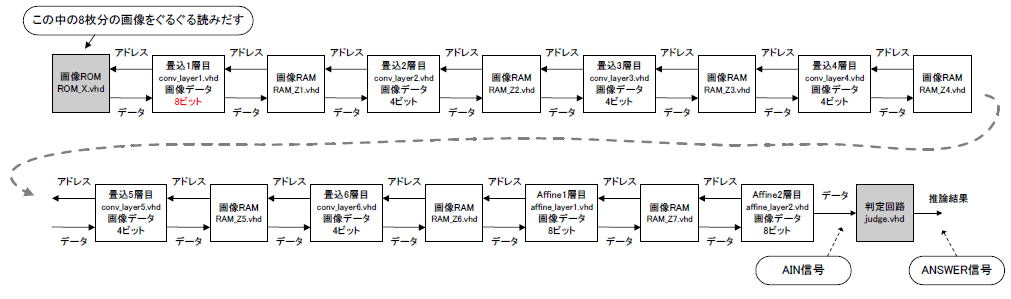

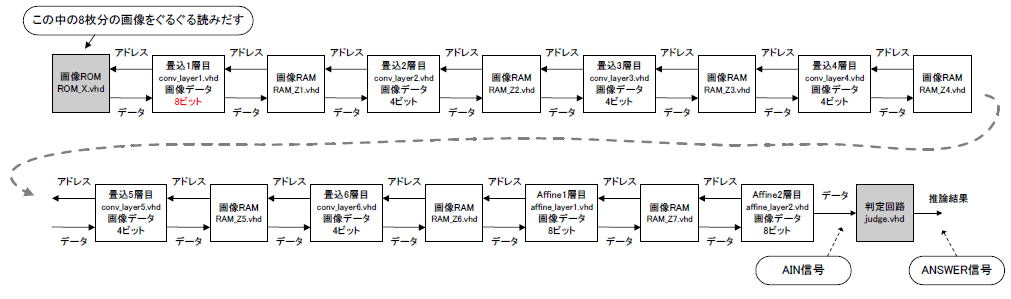

丂慜復偱偼乽忯傒崬傒僯儏乕儔儖僱僢僩儚乕僋乿偑FPGA偵廂傑傞傛偆夞楬婯柾傪嶍尭偟傑偟偨丅偦偺僽儘僢僋恾傪恾12-01偵帵偟傑偡丅夋憸ROM偺拞偵偼MNIST偺嵟弶偺8枃偺夋憸僨乕僞偑擖偭偰偍傝丄偦傟傜傪孞傝曉偟撉傒弌偟偰忯傒崬傒1憌栚偺擖椡偲偟傑偡丅

丂嵟屻偺敾掕夞楬偺擖椡AIN偵偼Affin2憌栚偺寢壥偑擖椡偝傟傑偡丅敾掕夞楬偺弌椡ANSWER偐傜偼悇榑寢壥乮0偐傜9傑偱偺抣丄4價僢僩乯偲側傝丄FPGA偺奜晹偵弌椡偝傟傑偡丅 |

丂丂恾12-01丂夋憸ROM偐傜偺8枃偑孞傝曉偟悇榑偝傟傞

仠FPGA傪僆僔儘偱偁偨偭偰悇榑寢壥傪尒傞

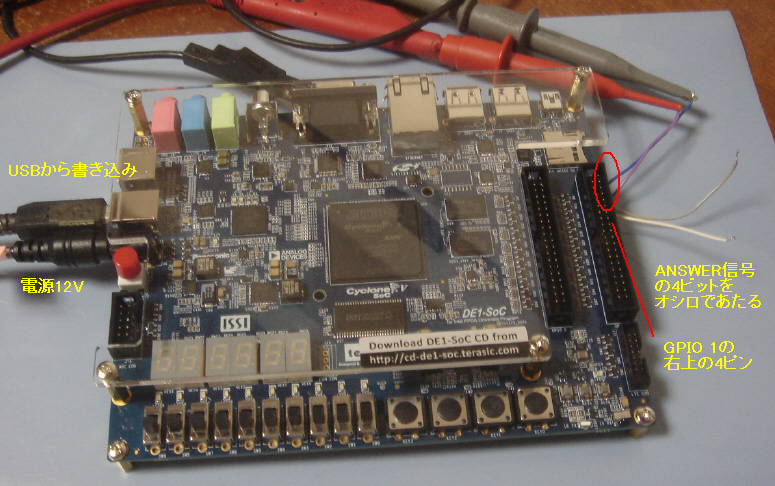

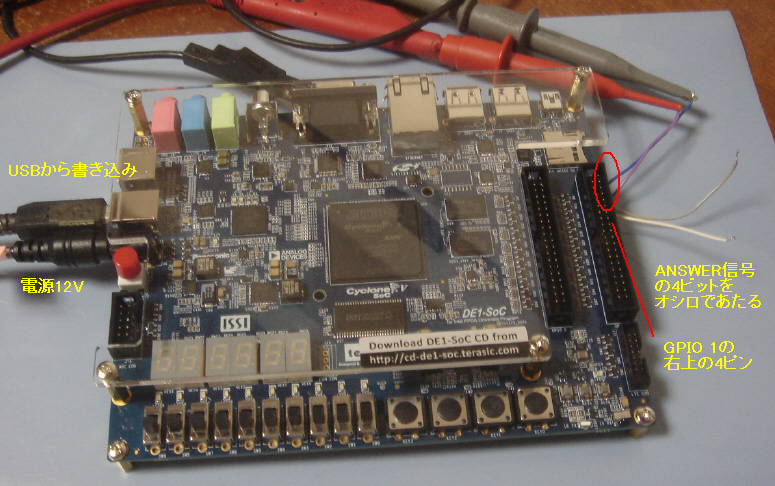

丂FPGA偼Intel幮偺CycloneV側偺偱丄Quartus Prime偲偄偆僣乕儖偱僾儘僕僃僋僩傪嶌惉偟丄僐儞僷僀儖偺屻丄彂偒崬傒傑偡乮偦偺庤弴偼偙偙乯丅幨恀12-01偺傛偆偵僐僱僋僞GPIO 1偺塃忋偺4僺儞偐傜ANSWER怣崋偑弌偰偒傑偡丅 |

丂丂幨恀12-01丂Terasic幮偺DE1-SoC傪偙偺傛偆偵僙僢僩傾僢僾偟偰彂偒崬傓

仠僔儈儏儗乕僔儑儞捠傝偵摦偄偰偄傞両

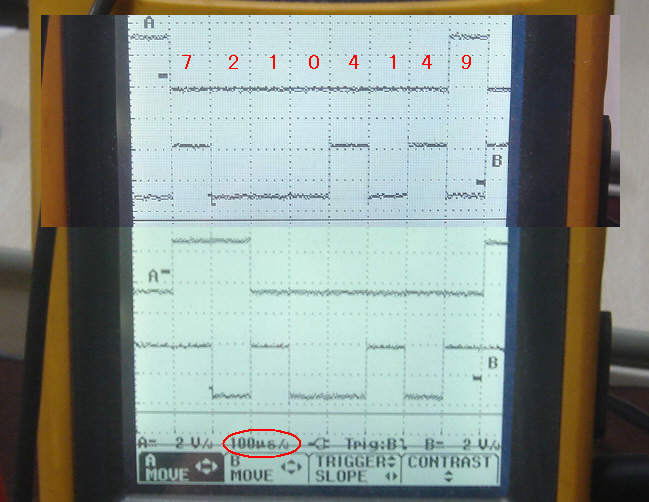

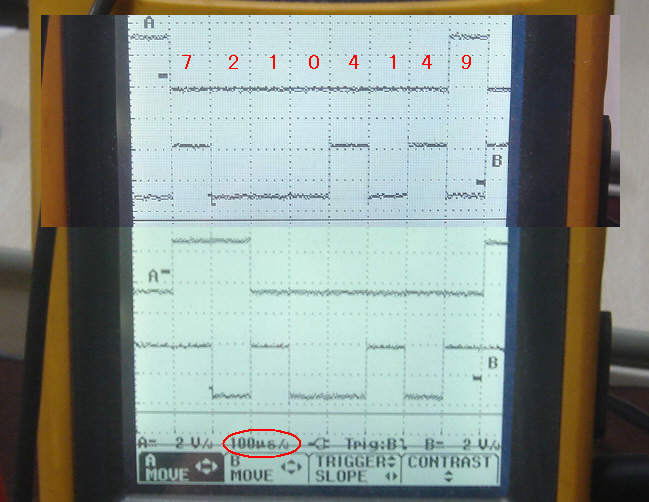

丂ANSWER怣崋傪僆僔儘偱妋擣偟偨傕偺偑幨恀12-02偱偡乮僾儘乕僽偑2杮偟偐側偄偺偱崌惉幨恀乯丅悇榑寢壥偼俈丆俀丆侾丆侽丆係丆侾丆係丆俋偲懕偒傑偡丅傑偨偦偺廃婜偼僔儈儏儗乕僔儑儞捠傝100us偵側偭偰偄傑偡乮仏侾乯丅

乮仏侾乯僋儘僢僋廃婜10ns亊10k僒僀僋儖偱僺僞儕100us丄忢偵偙偺抣偵側傞丅偙偺傛偆偵乽悇榑偵偐偐傞帪娫偑惓妋偵尒愊傕傟傞乿偙偲偑FPGA偺嫮傒偱偁傞乮僷僜僐儞傗儔僘儀儕乕僷僀偱偼偙偆偼側傜側偄乯 |

丂丂幨恀12-02丂惓偟偄悇榑寢壥偑100us廃婜偱弌偰偔傞

仠Python偲摨偠偙偲偑FPGA撪晹偱婲偙偭偰偄傞

丂恾12-02偼摨偠悇榑傪Python偱峴偭偨寢壥偱偡丅忯傒崬傒僯儏乕儔儖僱僢僩儚乕僋偱偼暋嶨側墘嶼傪峴偄傑偡偑丄強慒偼惍悢偺妡偗嶼偲懌偟嶼偱偡丅尵岅偑Python偩傠偆偑VHDL偩傠偆偑摨偠寢壥偵側傝傑偡丅偦偟偰VHDL傪FPGA偵惓偟偔僀儞僾儕偡傟偽摉慠寢壥偼堦抳偟丄惓夝棪傕摨偠乮98.53%)偵側傞偼偢偱偡丅 |

丂丂恾12-02丂Python偺寢壥偲妋擣乮Anaconda Jupyter Lab偱摦嶌乯

仠柍彏偱巊偊傞儘僕僢僋傾僫儔僀僓SignalTap偱FPGA撪晹傪尒傞

丂Quartus Prime偵偼SignalTap偲偄偆儘僕僢僋傾僫儔僀僓乮仏俀乯婡擻偑偁傝傑偡丅恾12-03偼Affine2憌栚偺弌椡AIN傪娤應偟偨傕偺偱偡丅俈亄侾斣栚偑堦斣戝偒偄偺偱ANSWER偼乫俈乫偵側傝傑偡丅恾12-02偺1峴栚偲僺僞儕堦抳偟偰偄傞偙偲傪妋擣偟傑偟傚偆丅

乮仏俀乯FPGA偺撪晹怣崋傪娤應偱偒傞僣乕儖丅巊偄曽偼偙偙丅 |

丂丂恾12-03丂MNIST偺1枃栚偼悢帤偺乫俈乫

| 丂恾12-04偼AIN偺2亄侾斣栚偑堦斣戝偒偄偺偱ANSWER偼乫俀乫偵側傝傑偡丅恾12-02偺2峴栚偲僺僞儕堦抳偟偰偄傞偙偲傪妋擣偟傑偟傚偆丅 |

丂丂恾12-04丂MNIST偺2枃栚偼悢帤偺乫俀乫

| 丂恾12-05偼AIN偺1亄侾斣栚偑堦斣戝偒偄偺偱ANSWER偼乫侾乫偵側傝傑偡丅恾12-02偺3峴栚偲僺僞儕堦抳偟偰偄傞偙偲傪妋擣偟傑偟傚偆丅 |

丂丂恾12-05丂MNIST偺3枃栚偼悢帤偺乫侾乫

| 丂恾12-06偼AIN偺0亄侾斣栚偑堦斣戝偒偄偺偱ANSWER偼乫侽乫偵側傝傑偡丅恾12-02偺4峴栚偲僺僞儕堦抳偟偰偄傞偙偲傪妋擣偟傑偟傚偆丅 |

丂丂恾12-06丂MNIST偺4枃栚偼悢帤偺乫侽乫

| 丂恾12-07偼AIN偺4亄侾斣栚偑堦斣戝偒偄偺偱ANSWER偼乫係乫偵側傝傑偡丅恾12-02偺5峴栚偲僺僞儕堦抳偟偰偄傞偙偲傪妋擣偟傑偟傚偆丅 |

丂丂恾12-07丂MNIST偺5枃栚偼悢帤偺乫係乫

| 丂恾12-08偼AIN偺1亄侾斣栚偑堦斣戝偒偄偺偱ANSWER偼乫侾乫偵側傝傑偡丅恾12-02偺6峴栚偲僺僞儕堦抳偟偰偄傞偙偲傪妋擣偟傑偟傚偆丅 |

丂丂恾12-08丂MNIST偺6枃栚偼悢帤偺乫侾乫

| 丂恾12-09偼AIN偺4亄侾斣栚偑堦斣戝偒偄偺偱ANSWER偼乫係乫偵側傝傑偡丅恾12-02偺7峴栚偲僺僞儕堦抳偟偰偄傞偙偲傪妋擣偟傑偟傚偆丅 |

丂丂恾12-09丂MNIST偺7枃栚偼悢帤偺乫係乫

| 丂恾12-10偼AIN偺9亄侾斣栚偑堦斣戝偒偄偺偱ANSWER偼乫俋乫偵側傝傑偡丅恾12-02偺8峴栚偲僺僞儕堦抳偟偰偄傞偙偲傪妋擣偟傑偟傚偆丅 |

丂丂恾12-10丂MNIST偺8枃栚偼悢帤偺乫俋乫

栚師傊栠傞 |