11-03 畳み込み2〜6層目の重み係数を2ビットにする

前節では2層目以降の画像データのビット数を4として回路規模を減らしました。本節では「重み係数」に注目して更に回路を小さくします。

●係数の数が膨大なのに注目

表11-21に各層の重み係数の数を示します。畳み込み1層目、Affine1層目、Affine2層目の係数は-256〜+255までの任意の値をとり得るのに対し、畳み込み2〜6層目までの係数は-64, -16, +16, +64の4種類に限定されます。 |

表11-21 各層の重み係数の数。灰色の層は4種類(-64, -16, +16, +64)のみとり得る

| 畳込1層目 |

畳込2層目 |

畳込3層目 |

畳込4層目 |

畳込5層目 |

畳込6層目 |

Affine1層目 |

Affine2層目 |

| 144 |

2,304 |

4,608 |

9,216 |

18,432 |

36,864 |

51,200 |

500 |

●重み係数ROMの記述に無駄が多い

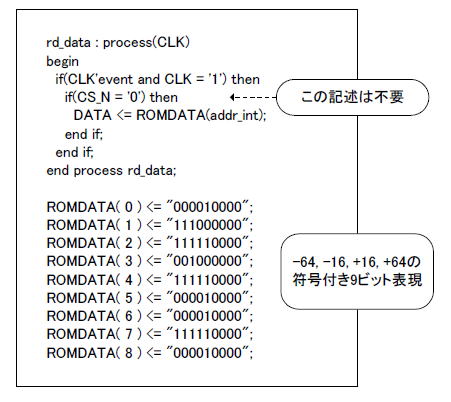

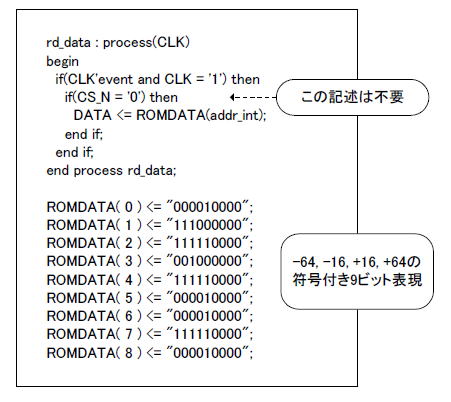

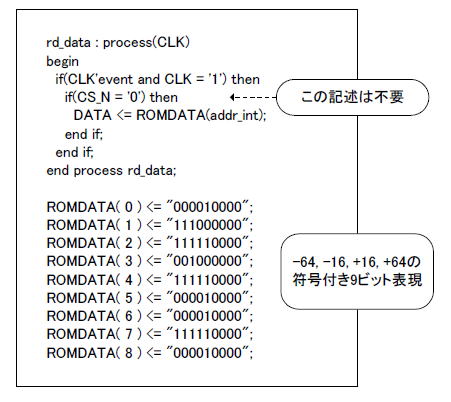

リスト11-21は畳み込み2層目の係数ROMの記述です。このように各データは即値(-64,

-16, +16, +64の符号付き9ビット表現)になっています。

またCS_Nは常に0で使用するので、この記述をとると多少回路を減らせる可能性があります。 |

リスト11-21 ROM_W2_00.00.vhdの一部(変更前)。各データは9ビット

●4種類しかないのだから9ビットもいらないはず

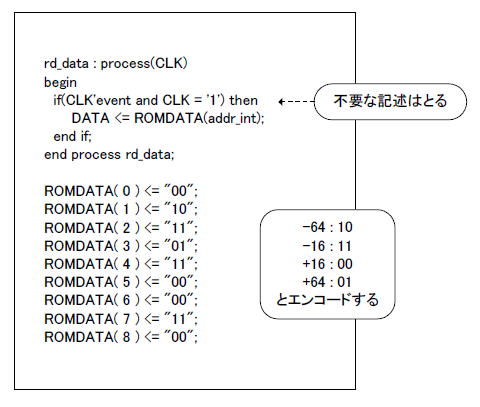

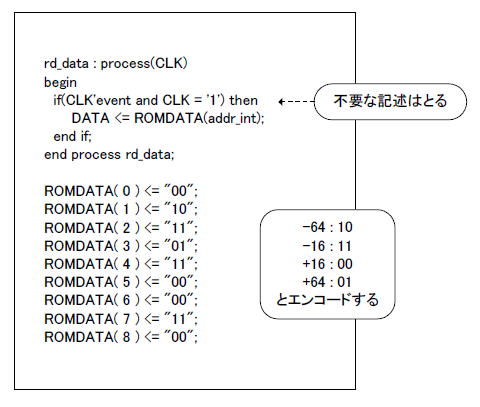

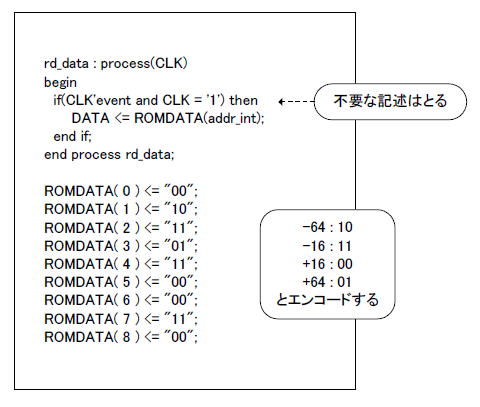

係数値は4種類しかないため、それらを表現するには2ビットで十分です。したがってリスト11-22のように対応させてROMデータとします(*1)。また不要な記述(CS_N)は削除してすっきりさせます。係数の数は膨大(表11‐21)なので、こうすれば回路をだいぶ減らせそうです。

(*1)ROMのように記述しているが、要素数が9個と少ないため合成すると論理素子に割り当てられる。 |

リスト11-22 ROM_W2_00.00.vhdの一部(変更後)。各データは2ビット

●2ビット化した係数でちゃんと動くか確認

図11-21はtb_conv_hw/conv_hw_1/conv_layer2_inst/CL2_00_inst/dotpro_sft_00/SHIFTMUL_inst以下の信号です。COEFFとPIXDATAの乗算結果がMULOUTになります。係数COEFFが1なら(+4)倍、0なら(+1)倍、-1なら(-1)倍、-2なら(-4)倍になっています(*2)。

(*2)本来係数は±16、±64なのでもう16倍する必要があるが、そのぶんはこのプロセスで調整する。

|

図11-21 COEFF=-2は-4倍、-1は-1倍、0は+1倍、1は+4倍を意味する

次のページへ

目次へ戻る |