●ビット数を減らして乗算や加算を行う

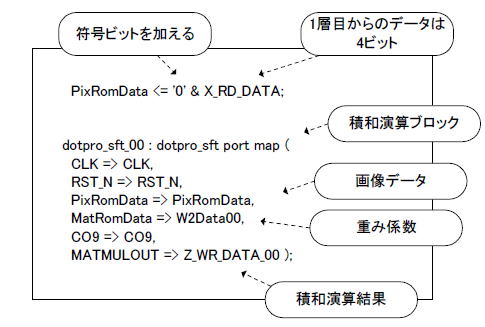

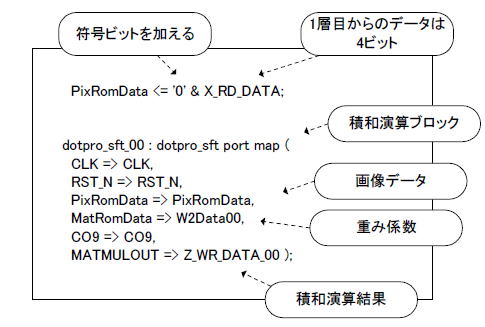

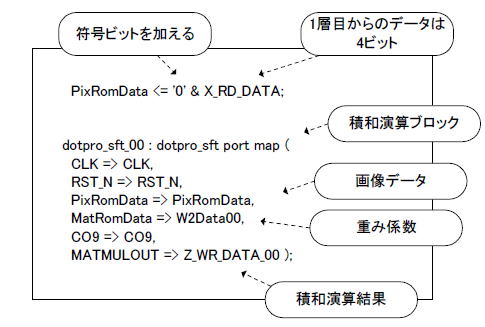

畳み込み2層目の積和演算の部分のVHDLをリスト11-11に示します。X_RD_DATAは1層目からの画像データ(8→4ビットに削減)、それに符号ビットを付加してPixRomDataは5ビットになり、積和演算器に入力されます。入力のビット数が減ったぶん、積和演算器内の乗算、加算のビット数も減らせます。 |

リスト11-11 5ビットの画像データを積和演算器に入力

●ビット数を減らしたらシミュレーションで確認

畳み込み2層目の積和演算の部分のシミュレーションを見てみましょう。図11-17はtb_conv_hw/conv_hw_1/conv_layer2_inst/CL2_00_inst/Z_WR_DATA_XXです。Z_WR_DATA_00は5,

-3, 3, 2, ... となっています。 |

図11-17 畳み込み2層目の信号を見てみる

●EXCELの値はHDLの16倍になる

図11-18はconv_layer2.xlsm(畳み込み2層目)のim2col00_W2シートです。上図のZ_WR_DATA_00に16をかけた値、80, -48, 48, 32, ... となっています(*1)。

(*1)これらの下位4ビットは常に0、すなわち無駄なビットになるので、HDLでは省略した結果5,

-3, 3, 2, ... となった。 |

図11-18 EXCELはHDLの16倍の値になっている

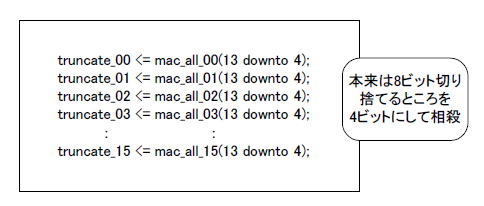

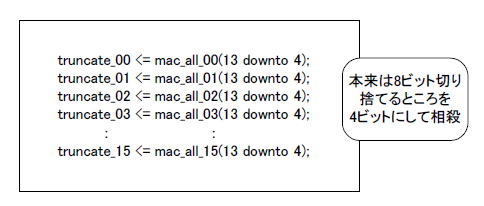

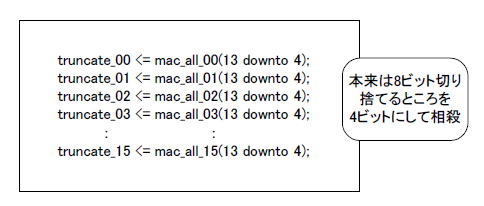

●8ビット切り捨てるところを4ビットにすればEXCELと合う

EXCELとHDLの齟齬はtb_conv_hw/conv_hw_1/conv_layer2_inst/truncate_XX信号で下位ビットを切り捨てる際に相殺します(*2)。

(*2)積和演算の後は従来、8ビット右シフトしていたが(ここにその理由)、4ビット右シフトにとどめる |

図11-19 8ビット捨てるところを4ビットにとどめる

●論理合成で回路が小さくなることを確認

図11-20はビット削減後の論理合成結果です。変更前はLogic utilizationが38k、変更後はそれが24kとなったので、回路規模は4割近く減ったことになります。 |

図11‐20 画像データを4ビットにした論理合成結果

●回路が膨大になる一因は積和演算器の数

各層の積和演算器の数を表11-01に示します。畳み込み2〜6層目で1024個もあるので、それにかかるビット数を削減すればかなりの回路削減に繋がります。

また図11‐20のTotal DSP Blocksは24になっていますが、これらは畳み込み1層目、Affine2層目、Affine3層目で使用しています(16+7+1=24個)。他の層はビットシフト型乗算なのでDSPは使用しません。 |

表11-01 各層の積和演算器の数。灰色の層の回路規模を削減した

| 畳込1層目 |

畳込2層目 |

畳込3層目 |

畳込4層目 |

畳込5層目 |

畳込6層目 |

Affine1層目 |

Affine2層目 |

| 16 |

256(ビットシフト型) |

128(ビットシフト型) |

256(ビットシフト型) |

128(ビットシフト型) |

256(ビットシフト型) |

7 |

1 |

●出来れば30%くらいの余裕を持たせたい

ロジックの使用量は76%となりましたが、最終的にはCMOSカメラ制御回路やVGAコントローラ、NiosIIマイコンなども追加するのでもう少し減らしたいところです。 |

最初のページへ

目次へ戻る |