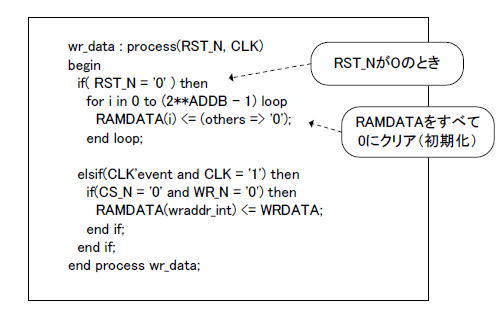

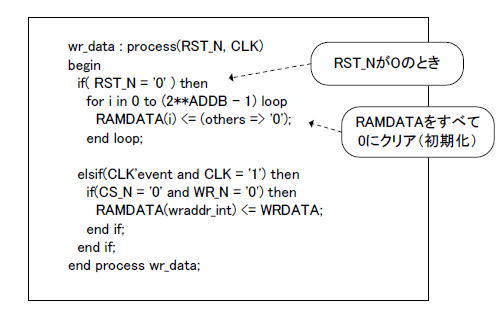

リスト11-01 RST_N信号でRAMDATAを初期化している・・・この部分を削除する

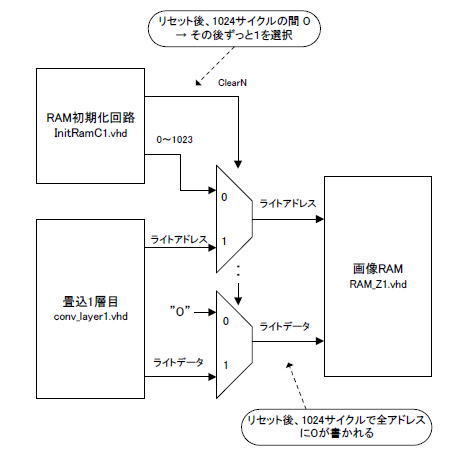

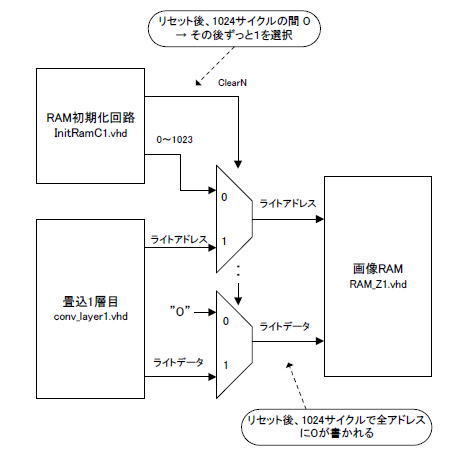

図11-03 新たにRAM初期化回路を追加

図11-04 RST_Nの後に一回だけRAMデータがクリアされる

図11-05 FPGA内部RAMを使うと容量的に効率が良くなる 最初のページへ 目次へ戻る |

||||||||||||||||

リスト11-01 RST_N信号でRAMDATAを初期化している・・・この部分を削除する

図11-03 新たにRAM初期化回路を追加

図11-04 RST_Nの後に一回だけRAMデータがクリアされる

図11-05 FPGA内部RAMを使うと容量的に効率が良くなる 最初のページへ 目次へ戻る |

||||||||||||||||