11-01 RAMのリセットの削除と初期化回路の追加

第1部では「全結合型ニューラルネットワーク」を「ZYBO Zynq7000」というFPGAボードに書き込みましたが、「畳み込みニューラルネットワーク」は回路規模が大きくなるので違うボードに書き込むことにします。

●DE1-SoCというFPGAボードに書き込む

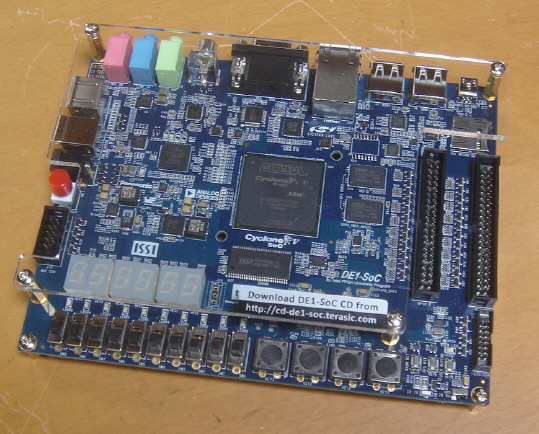

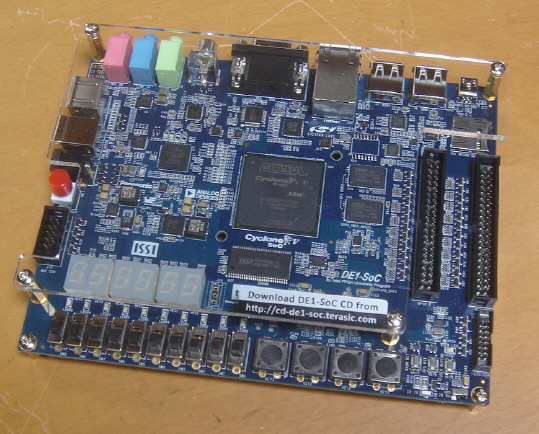

第3部ではDE1-SoCというTerasic社のFPGAボードを採用します(写真11-01)。日本円で3万円弱、FPGAはIntel(旧Altera)社のCycloneVシリーズです。このボードを採用した理由は以下の通り。

①ロジック部の容量が大きい。

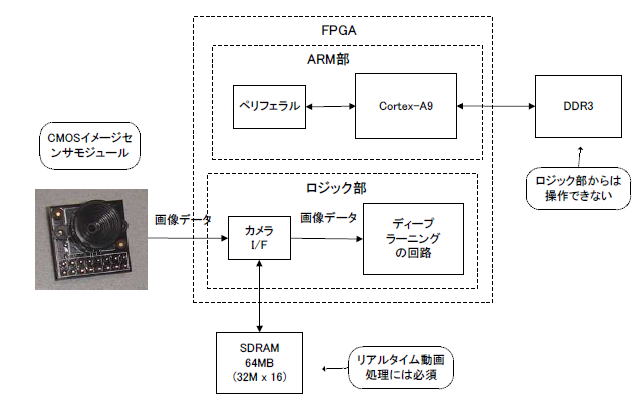

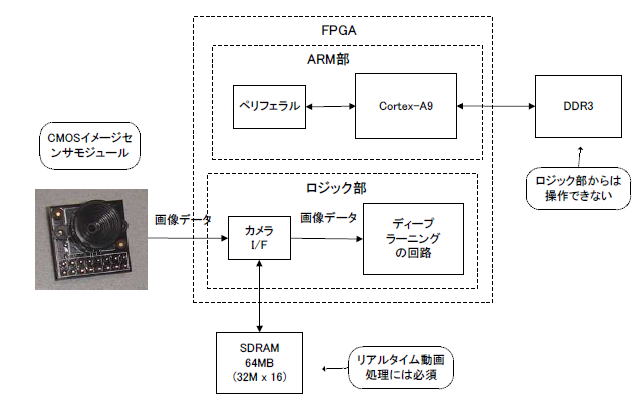

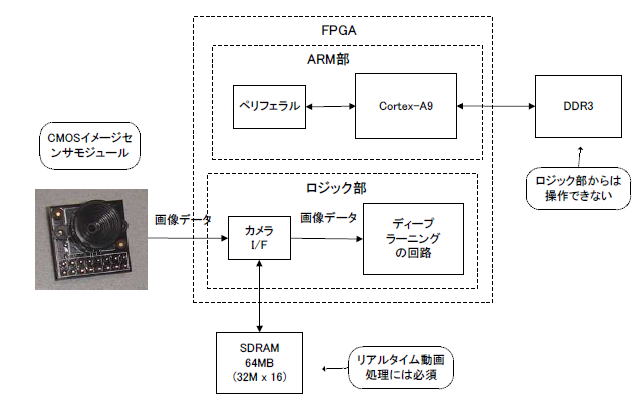

②ロジック部が直接操作できるSDRAM(64MB=32Mx16)が搭載されている(図11‐01)。 |

写真11-01 Terasic社のDE1-SoC。Intel社CycloneV(5CSEMA5F31C6)搭載

●ロジック部が大きくてSDRAMが使えるDE1-SoC

ZYBO Zynq7000はXilinx社、DE1-SoCはIntel社とFPGAベンダーが違うので正確には比較できませんが、①に関しては後者の方が前者の5倍程度のロジック容量があるように見受けられます。

また最終的にCMOSカメラ(CMOSイメージセンサ)からの動画をリアルタイム認識する際、ロジック部が直接操作できるSDRAMが必須になります(図11-01)。前者はそれがなく(*1)、後者はそれがあります。

(*1)ZYBOにはDDR3が搭載されているが、それはARM Cortex-A9からしか操作できない。 |

図11-01 CMOSカメラからの動画をリアルタイム認識するのに適したDE1-SoC

■IntelのFPGAに書き込むにはQuartus Primeという開発環境を使う

FPGAに書き込む際に「論理合成」を行います。HDLをロジック(AND, OR, DF/FやRAMなど)のレベルに落とす作業であり、Quartus Prime 19.1 Lite Editionというツールを使用します(図11-02)。無償・無期限で使用できます。 |

図11-02 Quartus Primeの無償版ライトエディションを使う

次のページへ

目次へ戻る |