11-02پ@ڈô‚فچ‚ف2پ`6‘w–ع‚ج‰و‘œƒfپ[ƒ^‚ً4ƒrƒbƒg‚ةچيŒ¸

پ@‘Oگك‚إ‚حRAMƒٹƒZƒbƒg‚ج‹Lڈq‚ًچيڈœ‚µ‚ؤ‰ٌکH‹K–ح‚ًŒ¸‚炵‚ـ‚µ‚½‚ھپA‚ـ‚¾ƒچƒWƒbƒN•”—e—ت‚ج100پ“‚ً’´‚¦‚ؤ‚¢‚ـ‚·پB

پœ‰و‘œƒfپ[ƒ^‚ح–{“–‚ة8ƒrƒbƒg‚à•K—v‚ب‚ج‚©پH

پ@‚±‚جژ“_‚إ‰و‘œƒfپ[ƒ^‚ًگ®گ”‰»‚µ‚ـ‚µ‚½‚ھپA‚»‚جƒrƒbƒgگ”‚ح‚W‚إ‚ ‚èپA0پ`255‚ـ‚إ‚ج’l‚ً‚ئ‚蓾‚ـ‚µ‚½پB

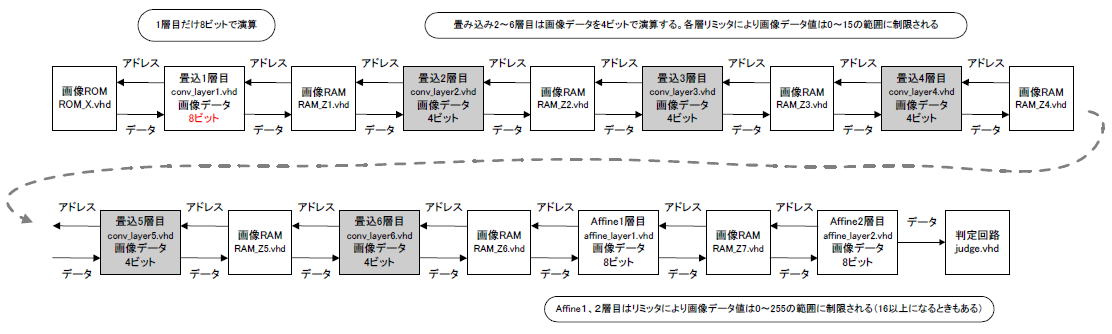

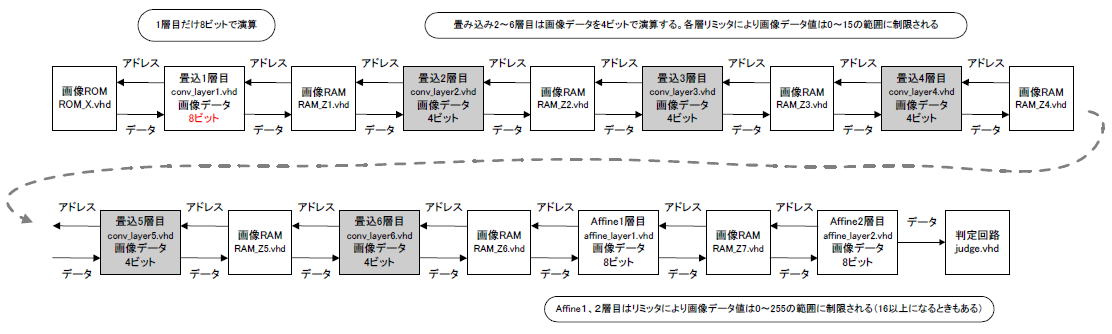

پ@‚ـ‚½‚±‚جژ“_‚إڈô‚فچ‚ف2‘w–عˆبچ~‚جڈd‚فŒWگ”‚ً4ژي—قپi-64, -16, +16, +64)‚ةچi‚è‚ـ‚µ‚½پB‚»‚ê‚ًٹس‚ف‚é‚ئپA‰و‘œƒfپ[ƒ^‚جƒrƒbƒgگ”‚ًچيŒ¸‚µ‚ؤ‚à”Fژ¯—¦‚ھ—ژ‚؟‚ب‚¢‰آ”\گ«‚ھ‚ ‚è‚ـ‚·پB‚»‚±‚إگ}11-11‚ج‚و‚¤‚ة2‘w–عˆبچ~‚ح‰و‘œƒfپ[ƒ^‚ً8ƒrƒbƒgپ¨4ƒrƒbƒg‚ئŒ¸‚ç‚·‚±‚ئ‚ًچl‚¦‚ـ‚·پB |

پ@پ@گ}11-11پ@ٹDگF‚ج‘w‚ج‰و‘œƒfپ[ƒ^‚جƒrƒbƒgگ”‚ًŒ¸‚炵‚ؤ‚ف‚é

پœƒrƒbƒgگ”‚ًŒ¸‚炵‚ؤ‚àگ³‰ً—¦‚ح‚ظ‚ئ‚ٌ‚ا•د‚ي‚ç‚ب‚¢پI

پ@گ³‰ً—¦‚حPython‚إٹm”F‚µ‚ـ‚·پBڈô‚فچ‚ف1‘w–ع‚ھڈI‚ي‚ء‚½ژ“_‚ج‰و‘œƒfپ[ƒ^‚ً8ƒrƒbƒgپ¨4ƒrƒbƒg‚ئچيŒ¸‚µ‚ؤ0پ`15‚ج”حˆح‚ةژû‚ك‚ـ‚·پB

پ@‰و‘œƒfپ[ƒ^‚ھˆب‘O‚ج1/16‚ة‚ب‚é‚ج‚إپAƒoƒCƒAƒX‚ج’l‚à1/16‚ة‚µ‚ؤƒŒƒxƒ‹چ‡‚ي‚¹‚µ‚ؤ‚©‚ç‘«‚µ‚±‚ف‚ـ‚·پB

پ@•دچX‚µ‚½PythonƒvƒچƒOƒ‰ƒ€‚ًAnacond Jupyter Lab‚إژہچs‚µ‚½Œ‹‰ت‚ًگ}11-12‚ةژ¦‚µ‚ـ‚·پBگ³‰ً—¦‚ح98.53پ“‚ئ‚ظ‚ئ‚ٌ‚ا•د‚ي‚è‚ـ‚¹‚ٌپiپ–‚PپjپB

پ@‚µ‚½‚ھ‚ء‚ؤ2‘w–عˆبچ~‚جƒrƒbƒgگ”‚ً8‚©‚ç4‚ةŒ¸‚炵‚ؤ‚à–â‘è‚ب‚¢‚±‚ئ‚ھ•ھ‚©‚èپA‰ٌکH‹K–حپiDF/F‚جگ”‚âRAM‚ج—e—تپj‚ھ‰½ٹ„‚©Œ¸‚点‚»‚¤‚إ‚·پB

پiپ–‚Pپjˆب‘O‚ح98.28پ“‚¾‚ء‚½‚ج‚إ‚ق‚µ‚ëژلٹ±ڈم‚ھ‚ء‚ؤ‚¢‚é |

پ@پ@گ}11-12پ@Python‚إƒeƒXƒg‰و‘œ‚ً10,000–‡”Fژ¯‚³‚¹‚ؤ9,853–‡گ³‰ً‚µ‚½

پœگدکa‰‰ژZŒم‚ة4ƒrƒbƒg‘½‚گط‚èژج‚ؤ‚é

پ@گدکa‰‰ژZ‚جŒم‚حڈ]—ˆپA8ƒrƒbƒg‰EƒVƒtƒg‚µ‚ؤ‚¢‚ـ‚µ‚½‚ھپi‚±‚±‚ة‚»‚ج——RپjپAconv_layer1.xlsmپiڈô‚فچ‚ف1‘w–ع)‚جtruncateƒVپ[ƒg‚ًŒ©‚é‚ئ12ƒrƒbƒg‰EƒVƒtƒg‚³‚ê‚ؤ‚¢‚ـ‚·پiگ}11-13)پB‚±‚ê‚ة‚و‚è‰و‘œƒfپ[ƒ^‚حڈ]—ˆ‚ج1/16‚ة‚ب‚è‚ـ‚·پB |

پ@پ@گ}11-13پ@conv_layer1.xlsm‚جtruncateƒVپ[ƒgپB8ƒrƒbƒgپ{4ƒrƒbƒgپپ12ƒrƒbƒg‰EƒVƒtƒg‚³‚¹‚é

پœƒٹƒ~ƒbƒ^‚ً‚©‚¯‚ؤ4ƒrƒbƒg‚ج”حˆح‚ةژû‚ك‚é

پ@‚»‚جŒمReluƒVپ[ƒg‚إƒٹƒ~ƒbƒ^‚ً‚©‚¯پAچإ‘ه’l‚ح15‚إ–Oکa‚µ‚ـ‚·پB‚±‚ê‚ة‚و‚è2‘w–عˆبچ~‚ج“ü—ح‰و‘œƒfپ[ƒ^‚ح4ƒrƒbƒgپA0پ`15‚ج”حˆح‚ةŒہ’肳‚ê‚ـ‚·(گ}11-14)پB |

پ@پ@گ}11-14پ@Reluٹضگ”‚ج‚ئ‚±‚ë‚إƒٹƒ~ƒbƒ^‚ً‚©‚¯‚é

پœ‰و‘œ‚ھ1/16‚ة‚ب‚ء‚½‚ج‚إƒoƒCƒAƒX‚à1/16‚ة‚·‚é

پ@گ}11-15‚حplusBiasƒVپ[ƒg‚إ‚·پB‰و‘œ‚جƒŒƒxƒ‹‚ھ1/16‚ة‚ب‚ء‚½‚±‚ئ‚ًٹس‚ف‚é‚ئپA‚»‚ج‚ـ‚ـƒoƒCƒAƒX‚ً‘«‚·‚ئ‚»‚ج‰e‹؟—ح‚ھ16”{‚ة‚ب‚ء‚ؤ‚µ‚ـ‚¢‚ـ‚·پB‚µ‚½‚ھ‚ء‚ؤƒoƒCƒAƒX‚à1/16‚ة‚µ‚ؤ‚©‚ç‰ءژZ‚µ‚ـ‚·پB |

پ@پ@گ}11-15پ@plusBiasƒVپ[ƒgپBƒoƒCƒAƒX‚à1/16‚ة‚·‚é

پœAffine2‘w–ع‚جŒ‹‰ت‚ًٹm”F

پ@گ}11-16‚حچإŒم‚جaffine_layer12.xlsmپiAffine2‘w–عپj‚جCalculateƒVپ[ƒg‚إ‚·پBa8‚جچs‚ًŒ©‚é‚ئگ}11-12‚ج1”شڈم‚ج—ٌ‚ئƒsƒ^ƒٹˆê’v‚µ‚ؤ‚¢‚ـ‚·پB”»’茋‰تAnswer‚ح‚V‚ئ‚ب‚ء‚ؤ‚¨‚èپAگ³‰ً‚µ‚ؤ‚¢‚ـ‚·پiMNISTƒeƒXƒg‰و‘œ‚جچإڈ‰‚ج1–‡‚حپf‚VپfپjپB |

پ@پ@گ}11-16پ@affine_layer12.xlsm‚جCalculateƒVپ[ƒgپBPython‚ئŒ‹‰ت‚ھˆê’v‚·‚é

ژں‚جƒyپ[ƒW‚ض

–عژں‚ض–ك‚é |