●組み込めるレベルのAIチップの有力候補-FPGA

①30x30画素といった小さい範囲を認識する

これによって高価で大規模なFPGAを使わなくても認識が可能になります。

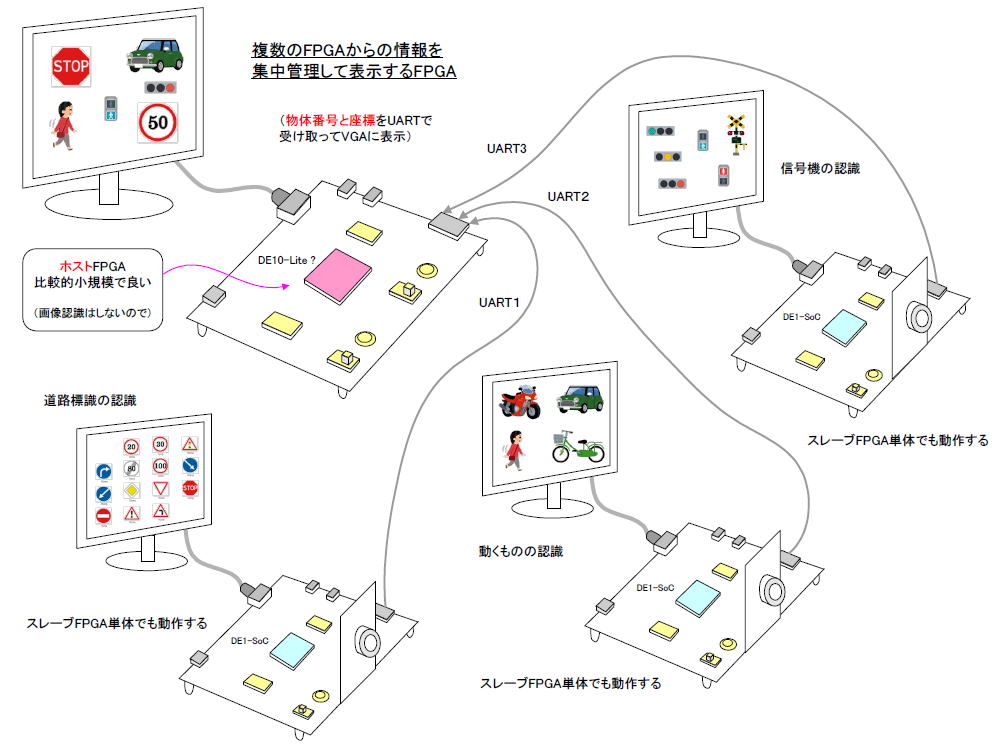

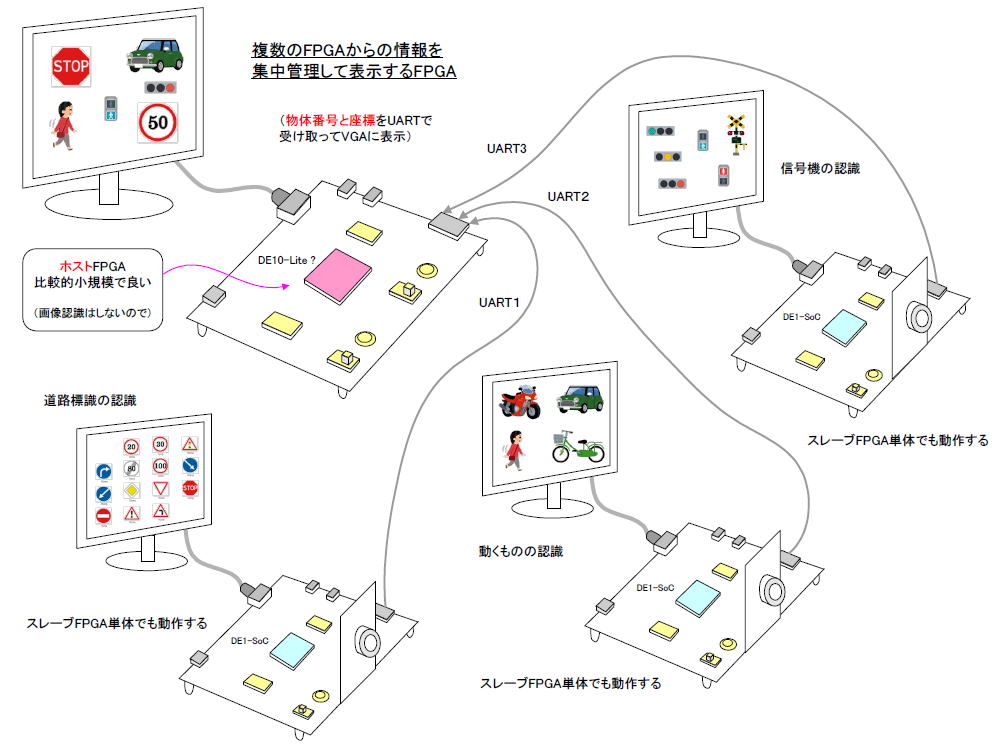

②一つのFPGAは一つの認識対象に専念する

このように認識対象を絞り込めば、更に小規模のFPGAで認識が可能になります。

③比較的小規模のFPGAを複数使い、認識対象を複数処理する

「大規模ななFPGAですべての認識対象を処理する」よりも価格的、消費電力的に有利になると思われます。

④集中管理はFPGAでもマイコンでも可能

図0-20ではホストFPGAがスレーブFPGAを統括管理しますが、VGAに映し出す必要が無ければ、ワンチップ・マイコンなどでも代替できると思います。

本企画ではこのように、FPGAを使ってディープラーニングのハードウエア化を行います。GPUなどと比べて低消費電力で放熱板も要らないので、電気製品に組み込むことも現実的になってきます。 |