2-04 3,4,5層目は係数を4種にしてROMを節約

●FPGAではROM(初期値付きRAM)が使える

FPGAにおいて係数はROMに格納されます。図2‐15に各層の係数の数を示します。

1層目と6層目は符号付き9ビットで整数化したので、ROMのビット数は係数の数×9になります。

2層目は係数を8種類に限定したのでROMのビット数は係数の数×3になります。 |

図2‐15 各層の係数の数。5層目が一番多い

●思い切って4種類に限定

係数は層が進むにつれて多くなり、特に5層目は262,144個となってROM容量を圧迫します。

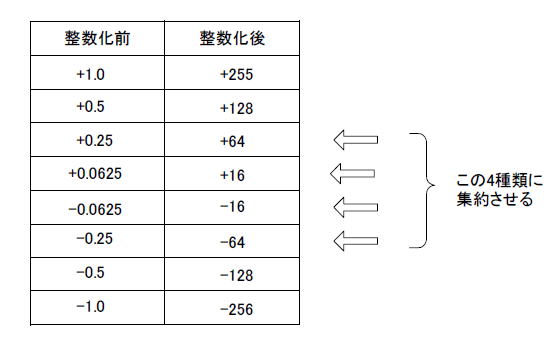

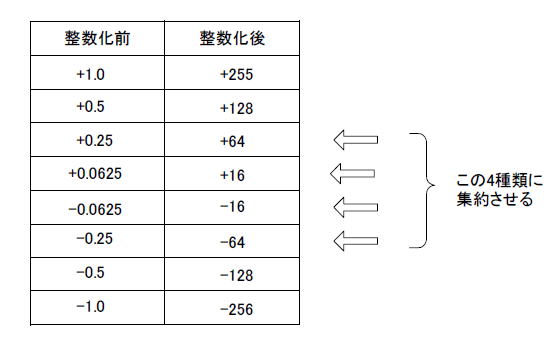

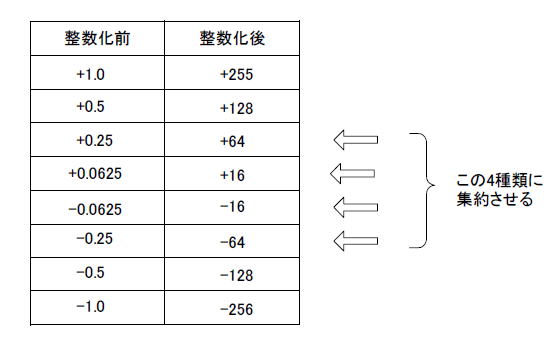

そこで図2‐16のように、3、4、5層目は係数を4種類にします(*1)。その場合ROMのビット数は係数の数×2となりなります。

(*1)「係数の数が多い」ということは「個々の係数の重要度は低い」ともいえる |

図2‐16 -64, -16, +16, +64の4種類

●48以下なら16、超えたら64に整数化

図2‐17は5層目を整数化する際のPythonコードです。このように適当に閾値をもうけて4種類に限定します。 |

図2‐17 w5.csv(小数)を読んで整数化。w5_int.csvにセーブ

●CSVファイルを見てみる

図2‐18はw5_int.csv(整数化後の5層目の係数)です。-64, -16, +16, +64の4種類になっています。 |

図2‐18 係数の数は多いが種類は4種のみ

●ROMやビットシフト乗算器の節約になる

2層目は係数の種類は8種類でしたが、3,4,5層目の重み係数は4種類としました。それだけでROMの容量をだいぶ節約できます。また「ビットシフトによる乗算」の回路もよりシンプルになります。 |

次のページへ

目次へ戻る

|