7‐04 2層目のRAMアクセス(書き方、1層目と比較)

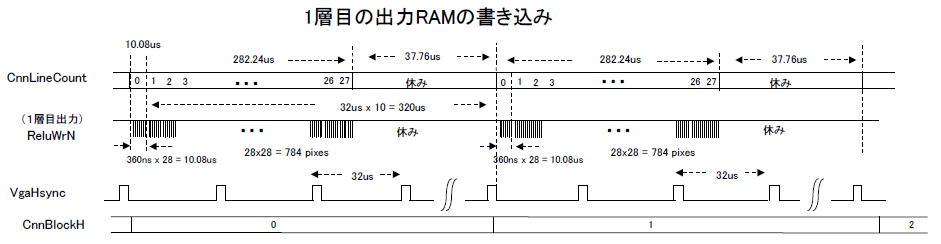

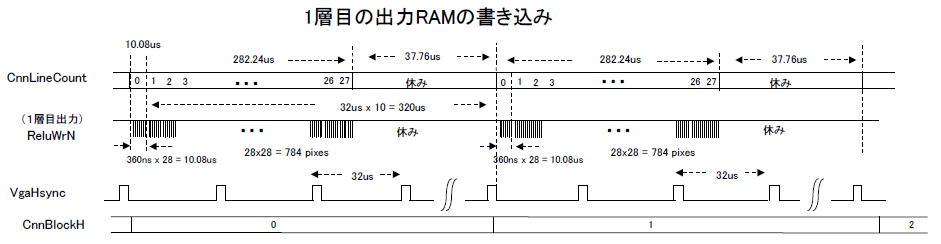

図7-25 ReluWrN(RAM書き込みイネーブル)に37.76usの休み時間がある

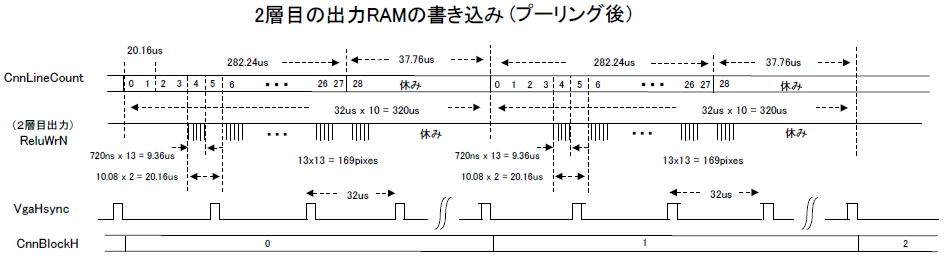

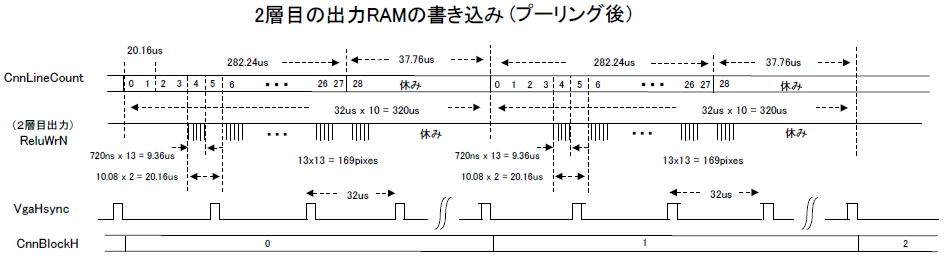

図7‐26 ReluWrN(RAM書き込みイネーブル)に隙間がある(プーリングにより)

次のページへ 目次へ戻る |

||||||

7‐04 2層目のRAMアクセス(書き方、1層目と比較)

図7-25 ReluWrN(RAM書き込みイネーブル)に37.76usの休み時間がある

図7‐26 ReluWrN(RAM書き込みイネーブル)に隙間がある(プーリングにより)

次のページへ 目次へ戻る |

||||||