7‐06 プーリングの回路とHDL

図7-50 プーリング前。26×26画素

図7-51 プーリング後(2層目の出力Ch0)。13×13画素

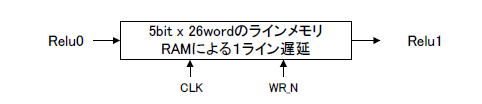

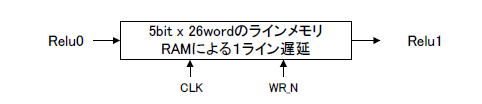

図7‐52 プーリングにはラインメモリが必要

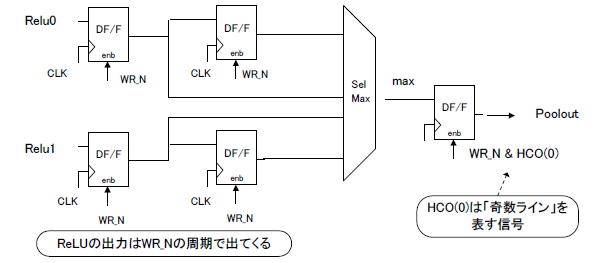

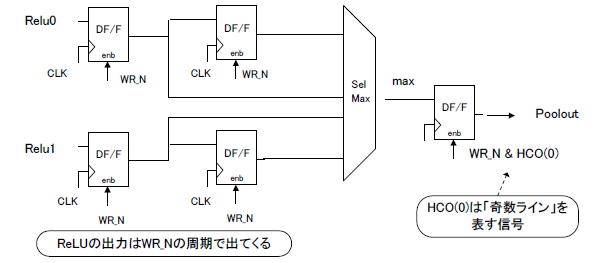

図7‐53 2×2画素の最大値を取り出す回路(pooling_max.vhd)

図7‐54 メモリ(図7‐52)とpooling_max(図7‐53)が32chぶんある (pooling_lay2.vhd)

最初のページへ 目次へ戻る |

||||||||||||

7‐06 プーリングの回路とHDL

図7-50 プーリング前。26×26画素

図7-51 プーリング後(2層目の出力Ch0)。13×13画素

図7‐52 プーリングにはラインメモリが必要

図7‐53 2×2画素の最大値を取り出す回路(pooling_max.vhd)

図7‐54 メモリ(図7‐52)とpooling_max(図7‐53)が32chぶんある (pooling_lay2.vhd)

最初のページへ 目次へ戻る |

||||||||||||