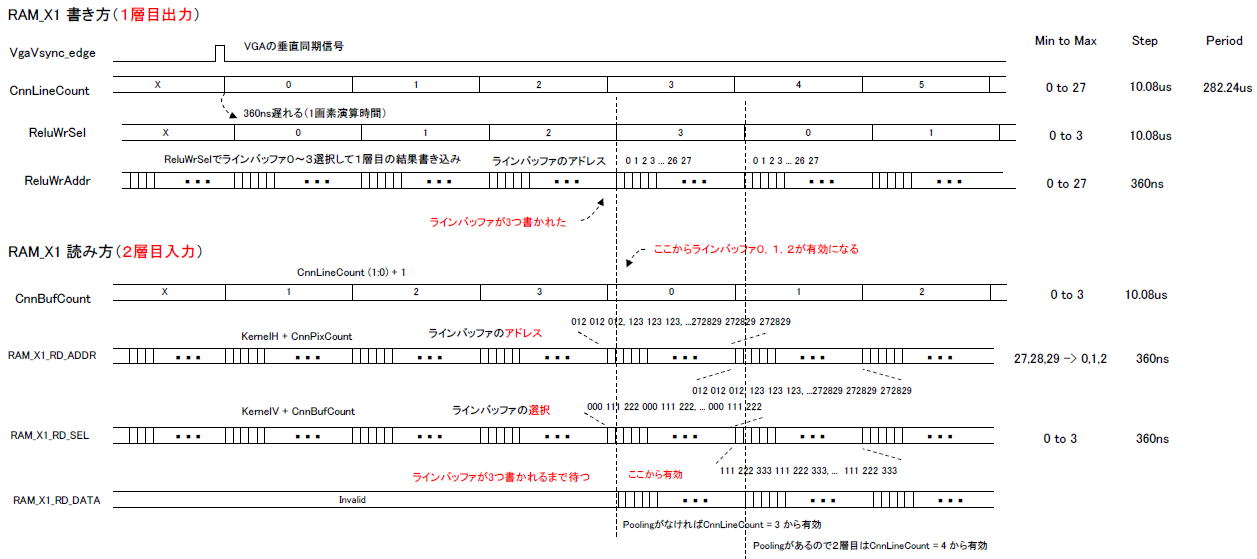

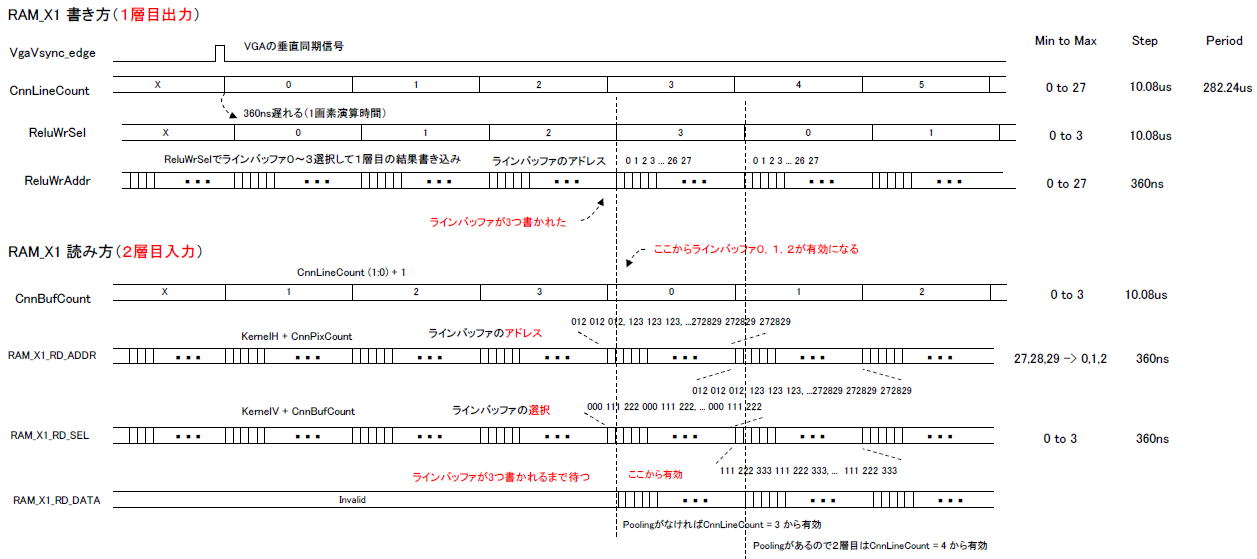

7پ]04پ@2‘w–ع‚جRAMƒAƒNƒZƒXپi“ا‚ف•ûپ^ڈ‘‚«•ûپA‘S‘ج‘œپj

گ}7-20پ@1‘w–ع‚ھڈ‘‚¢‚ؤ2‘w–ع‚ھ“ا‚ق‚و‚¤‚·

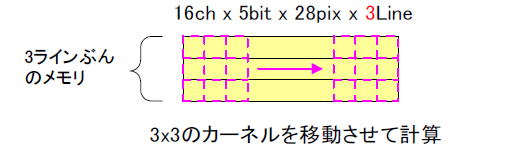

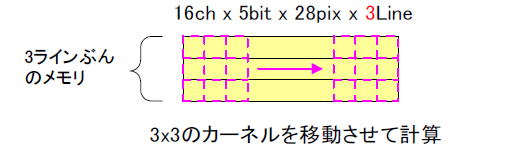

گ}7پ]21پ@ƒJپ[ƒlƒ‹‚ً‰E‚ة‚¸‚炵‚ب‚ھ‚烉ƒCƒ“ƒoƒbƒtƒ@“ا‚ق

ژں‚جƒyپ[ƒW‚ض –عژں‚ض–ك‚é |

|||||||

7پ]04پ@2‘w–ع‚جRAMƒAƒNƒZƒXپi“ا‚ف•ûپ^ڈ‘‚«•ûپA‘S‘ج‘œپj

گ}7-20پ@1‘w–ع‚ھڈ‘‚¢‚ؤ2‘w–ع‚ھ“ا‚ق‚و‚¤‚·

گ}7پ]21پ@ƒJپ[ƒlƒ‹‚ً‰E‚ة‚¸‚炵‚ب‚ھ‚烉ƒCƒ“ƒoƒbƒtƒ@“ا‚ق

ژں‚جƒyپ[ƒW‚ض –عژں‚ض–ك‚é |

|||||||