7‐04 2層目のRAMアクセス(読み方、詳細)

●入力4chを時分割で積和する

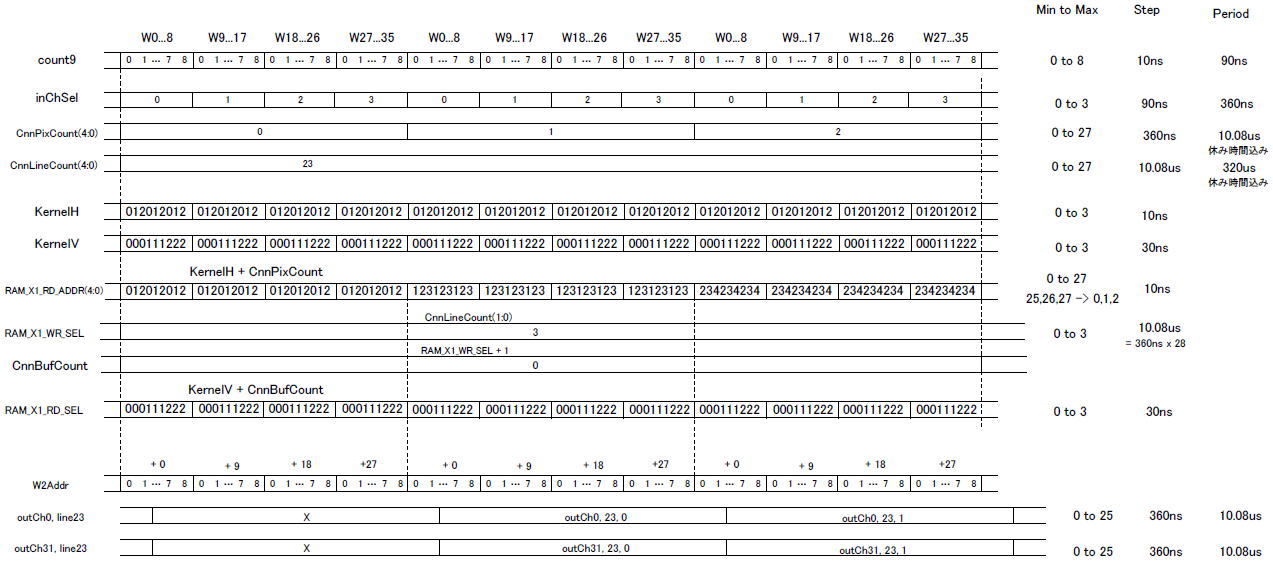

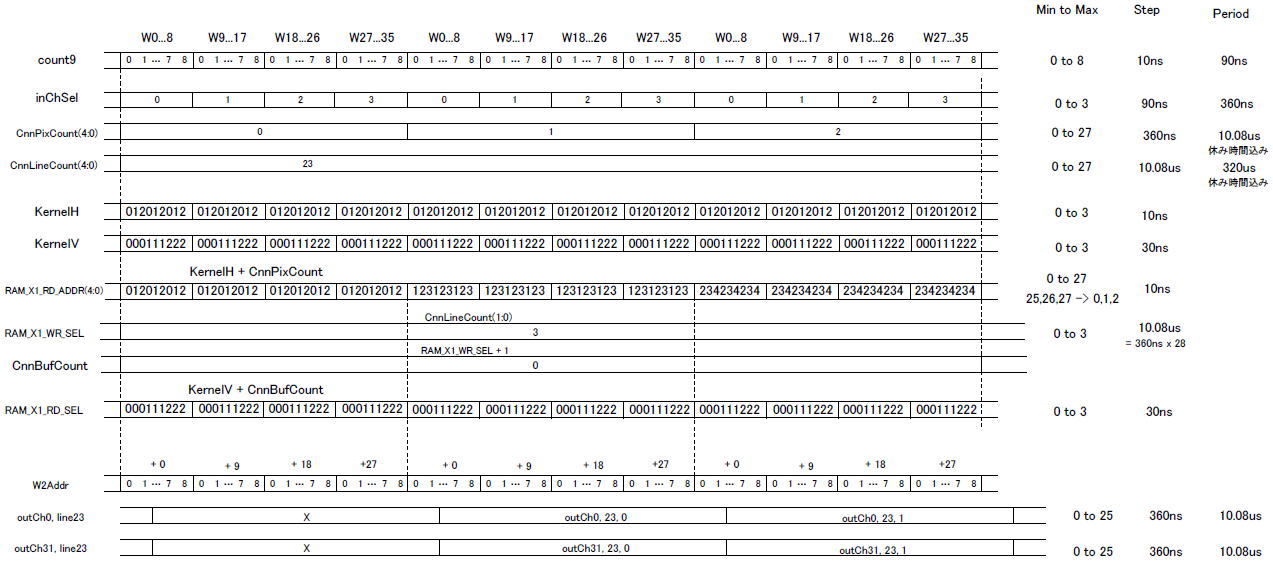

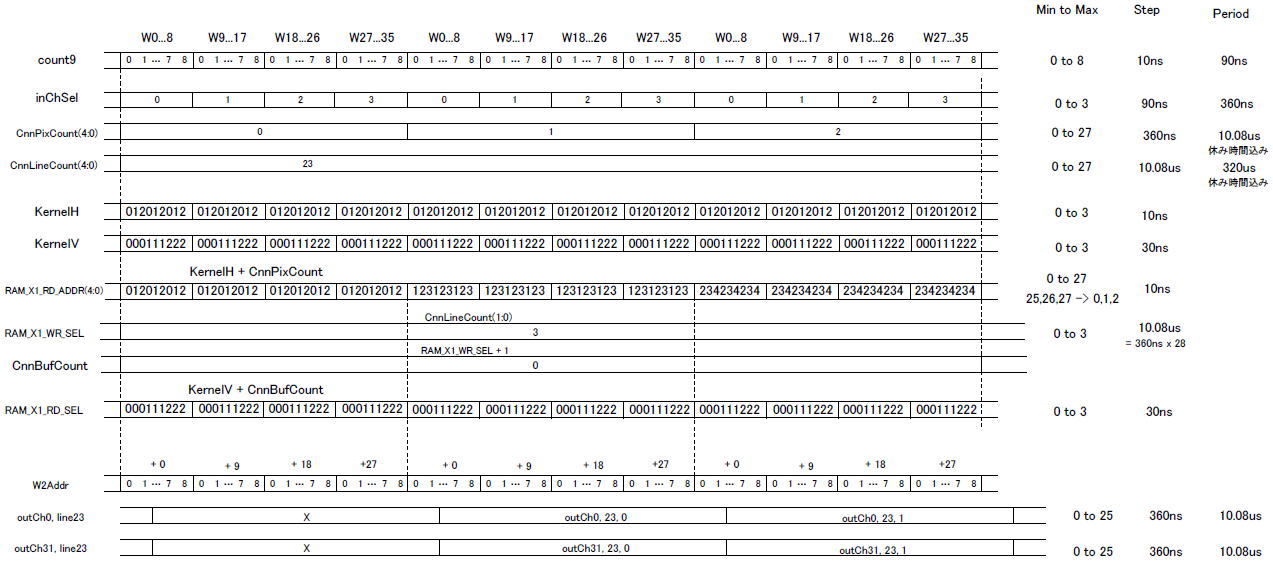

2層目はこのように入力4chを一つの積和演算器が受け持ちます。図7‐23のcount9のタイミングで3x3の画素が読み出されますが、入力が4chあるのでそれらを選択する必要があります。また入力Chに対応する係数も違います。したがってinChSelという信号でそれらを選択します。

出力の1画素を計算するのにかかる時間は90ns x 4ch = 360nsになります(CnnPixCountのステップ)。1ライン(26画素)計算するには360ns x 26 = 9.36usですが、1層目とライン単位で同期をとるため、休み時間を含めて10.08usになります(CnnLineCountのステップ)。

また1画面(26ライン)計算するのは10.08us x 262.08ですが、画面単位でも1層目と同期をとるため、休み時間含めて1画面320us(1層目と同じ)になります。 |

図7-23 RAMの読み出し(詳細)

●読み出しアドレスの作り方

2層目はRAM_X1を読みに行きますが、その読出しアドレスRAM_X1_RD_ADDRは図7‐23の中段、KernelH

+ CnnPixCountで生成します。またラインバッファの選択RAM_X1_RD_SELは同図のようにKernelV

+ CnnBufCountで生成します(*1)。

(*1)CnnBufCountはRAM_X1_WR_SEL(書き込みバッファ選択)に1を足したもの。そうすれば読み方は書き方を追いかけることができる

W2Addrは係数ROMのアドレスですが、+0, +9, +18, +27といったオフセットを与え、入力チャネルに対応した係数を読み出します。

|

●4つの乗算器で出力1チャネル計算

上記のようにラインバッファ、係数を読み出し、それらの積和をとります。ただしそれだけでは入力4chぶんの積和値でしかないため、この図のように4つの積和演算器の出力を足し込みます。

図7‐23の下の方、outCh0, 23, 0は出力ch0の23行目の最初の画素、outCh31, 23, 0は出力ch31の23行目の最初の画素という意味です。このようにoutCh0〜31まで並列で演算されます(*2)。

(*2)乗算器の数は4×32=128個なので128並列になる |

●乗算器の中身が変わるだけ

2層目は「ビットシフト型乗算器」を使いますが、それ以外は1層目と同じ積和演算回路/HDLになります。 |

次のページへ

目次へ戻る

|