6乚05丂1憌栚偺RAM傾僋僙僗乮撉傒曽乯

仠彂偒側偑傜撉傒弌偡偨傔偺僺儞億儞儌乕僪

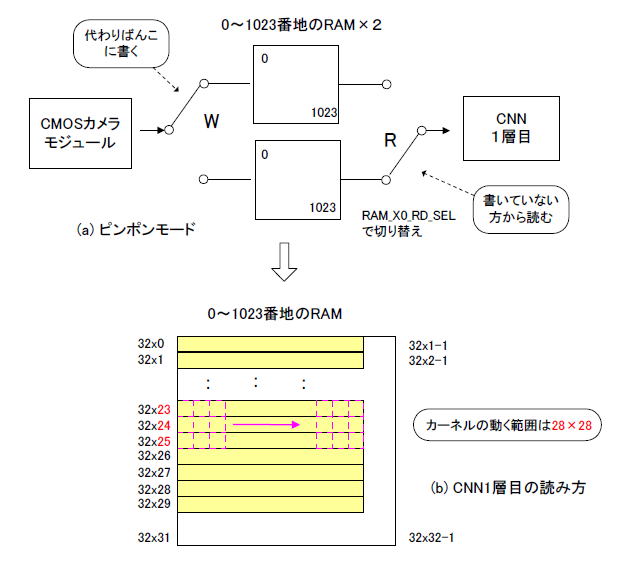

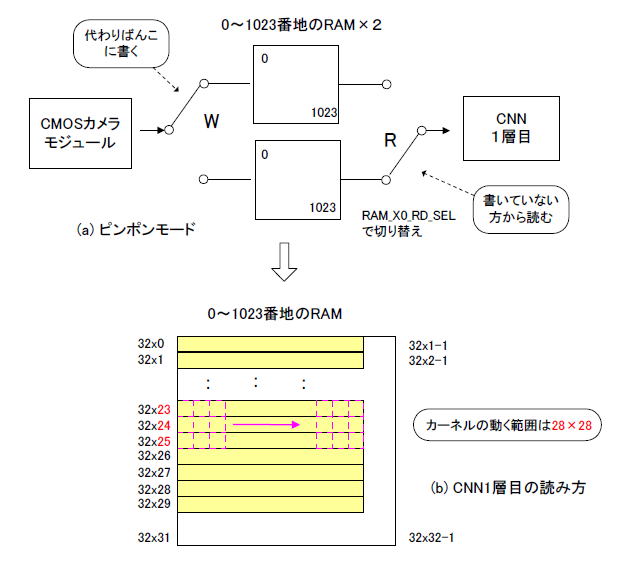

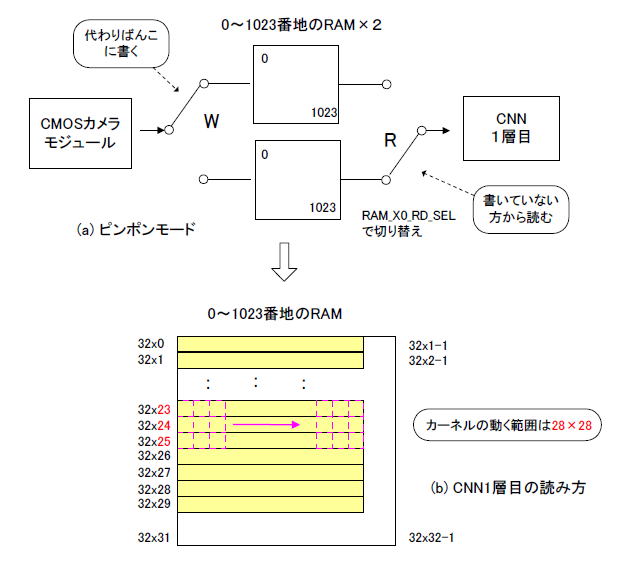

丂忯傒崬傒1憌栚偵偼RAM傪夘偟偰僨乕僞偑擖椡偝傟傑偡丅CMOS僇儊儔偐傜偺儕傾儖僞僀儉摦夋傪埖偆偨傔丄恾6乚21(a)偺傛偆偵乽僺儞億儞儌乕僪乿偱丄彂偄偰偄側偄曽偐傜撉傒弌偟傑偡丅

丂僺儞億儞備偊偵RAM偼2偮偁傝丄偦傟偧傟0乣1023乮32亊32乯斣抧傑偱偁傝傑偡乮仏侾乯丅CNN偺1僽儘僢僋30亊30側偺偱丄摨恾(b)偺傛偆偵夋柺偺塃偲壓偵乽寗娫乿偑偱偒傑偡丅

乮仏侾乯1憌栚偺擖椡偑擖傞RAM偼僼儗乕儉儊儌儕偵側傞丅俀丆俁丆係憌栚偺擖椡偑擖傞儊儌儕偼儔僀儞僶僢僼傽亊4偵側傞丅 |

恾6-21丂RAM偺斣抧傪2師尦揑偵峫偊傞

仠9夋慺撉弌偟仺9夋慺撉弌偟仺9夋慺撉弌偟乧傪孞傝曉偡

丂恾6乚21(b)偱偼3x3偺僇乕僱儖偑塃偵摦偔傛偆偡傪帵偟偰偄傑偡丅俋夋慺枅偺撉弌偟偼丒丒丒

丂23峴栚偺0, 1, 2楍仺丂24峴栚偺0, 1, 2楍仺丂25峴栚偺0, 1, 2楍仺

丂23峴栚偺1, 2, 3楍仺丂24峴栚偺1, 2, 3楍仺丂25峴栚偺1, 2, 3楍仺

丂23峴栚偺2, 3, 4楍仺丂24峴栚偺2, 3, 4楍仺丂25峴栚偺2, 3, 4楍仺 丒丒丒偲偄偭偨撉傒弌偟曽偵側傝傑偡丅

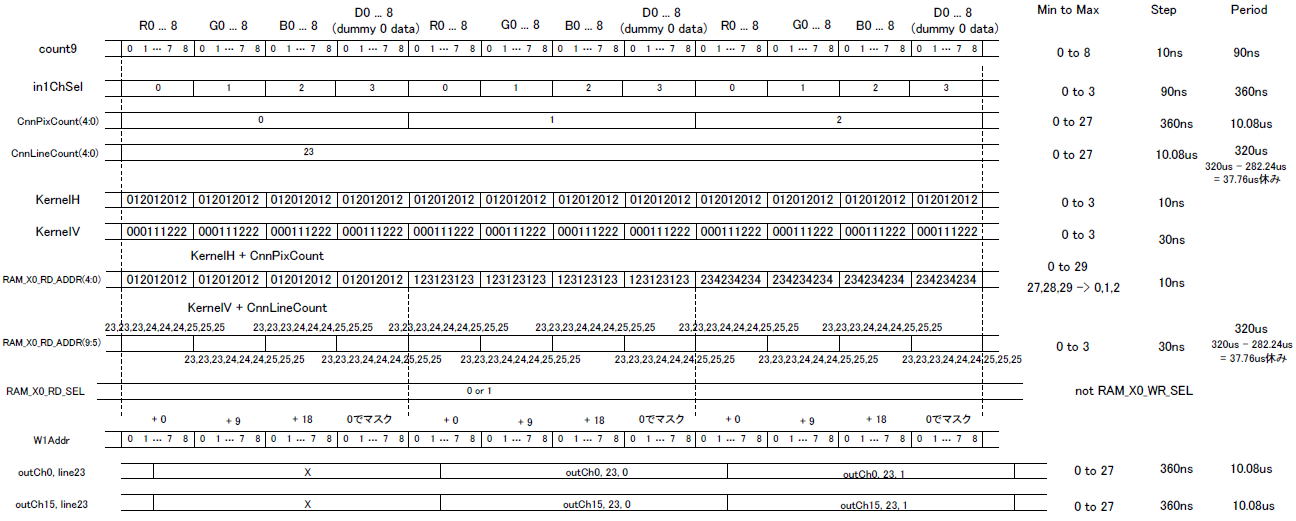

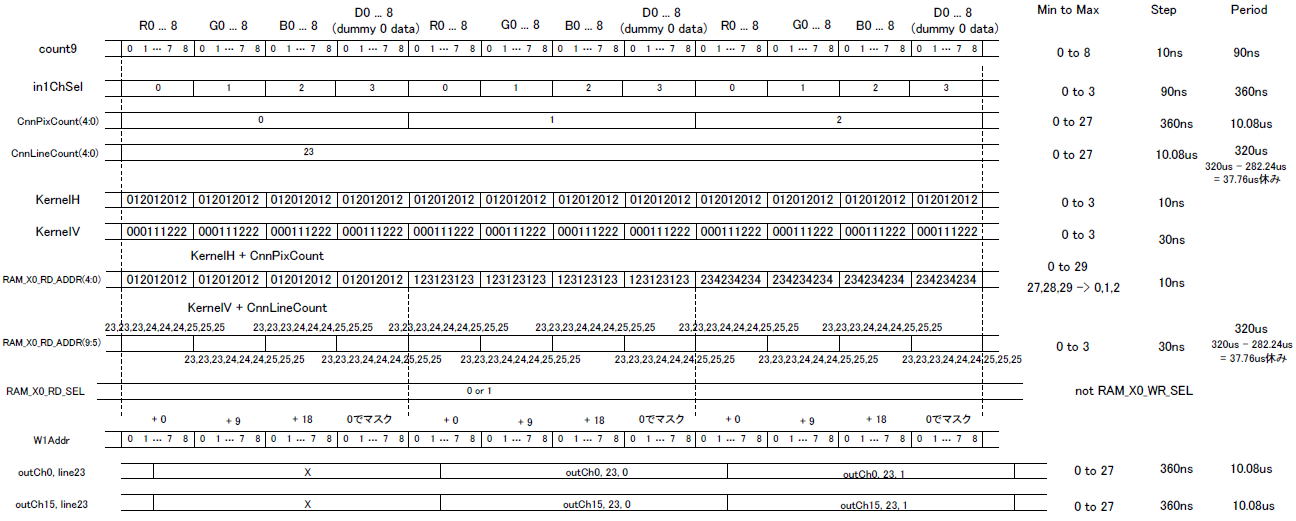

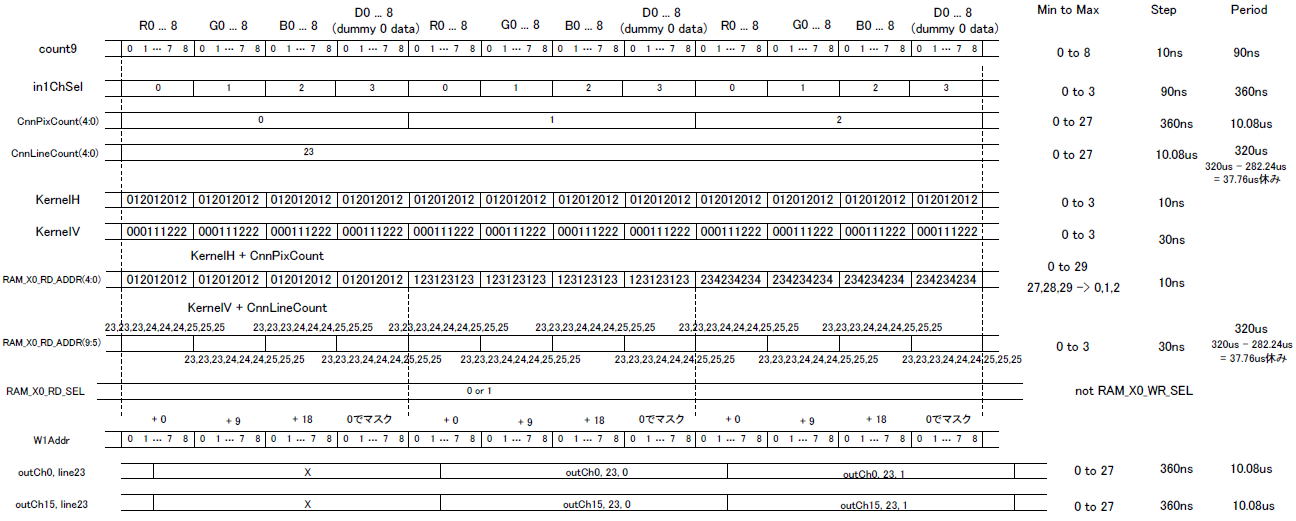

丂RAM偺撉弌偟傾僪儗僗RAM_X0_RD_ADDR偼恾6乚22偺傛偆偵惗惉偟傑偡丅傑偢KernelH偲偄偆怣崋偵CnnPixCount偲偄偆怣崋傪壛嶼偟丄偦傟傪傾僪儗僗偺壓埵5價僢僩偲偟傑偡丅師偵KernelV偵CnnLineCount傪壛嶼偟丄偦傟傪傾僪儗僗偺忋埵5價僢僩偟傑偡丅偦偆偡傟偽恾6乚21(b)偺傛偆側傾僪儗僢僔儞僌偑偱偒傑偡丅 |

恾6-22丂RAM傪撉傒弌偡偨傔偺傾僪儗僢僔儞僌

仠僺儞億儞儌乕僪偺慖戰怣崋

丂RAM_X0_RD_SEL偼恾6乚21(a)偺僺儞億儞儌乕僪偺RAM偺撉傒弌偟慖戰偵巊梡偟傑偡丅彂偒崬傒慖戰RAM_X0_WR_SEL偼偦偺媡榑棟偵側傝傑偡丅

仠RGB3ch傪偦傟偧傟學悢偲妡偗偰3ch椵愊偡傞

丂W1Addr偼廳傒學悢ROM偺傾僪儗僗偱偡丅擖椡3ch傇傫擖偭偰偍傝丄偦傟傜偺慖戰偼傾僪儗僗偵僆僼僙僢僩(0,

9, 18)傪壛嶼偡傞偩偗偱偡丅

丂側偍僟儈乕ch傕偁傞偺偱丄偦偺學悢偼0偱儅僗僋偟傑偡丅0偵偼壗傪偐偗偰傕0側偺偱丄係ch傇傫愊榓偟偨偲偟偰傕寢壥揑偵俁ch傇傫偺愊榓偵側傝傑偡丅 |

仠愊榓墘嶼婍16屄偱弌椡16ch暲楍墘嶼

丂outCh0, 23, 0偼弌椡ch0偺23儔僀儞丄0夋慺栚偺抣丄outCh0, 23, 1偼偦偺塃椬偺夋慺偺抣偱偡丅侾憌栚偺弌椡偼16ch偁傞偺偱愊榓墘嶼偑16暲楍偱峴傢傟丄弌椡ch0乣15偼摨帪偵墘嶼偝傟傑偡丅

仠僷僀僾儔僀儞摦嶌側偺偱擖椡偺帪娫偵崌傢偣偰弌椡

丂弌椡偺1夋慺傪墘嶼偡傞偺偵 10ns x 9 x 4ch = 360ns, 弌椡偺1儔僀儞傪墘嶼偡傞偺偵 360ns x 28 = 10.08us偐偐傝傑偡丅弌椡偺1夋柺偵偼 10.08us x 28 = 282.24us偐偐傝傑偡偑丄擖椡1夋柺偺帪娫320us偲崌傢偣傞偺偱丄媥傒帪娫傪娷傔偰320us偲側傝傑偡乮師儁乕僕嶲徠乯丅 |

師偺儁乕僕傊

栚師傊栠傞

|