11‐05 判定回路とHDL

●6層目の出力をもって判定する

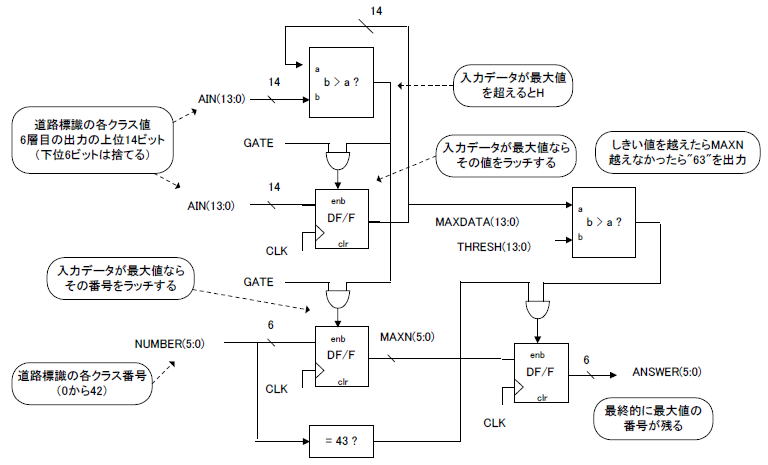

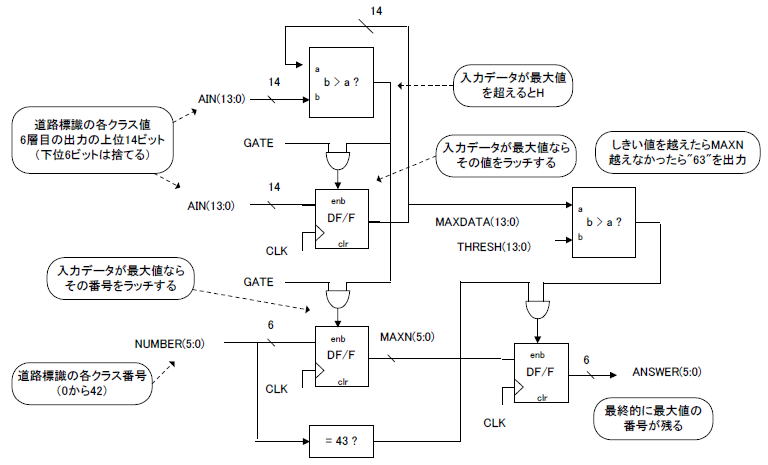

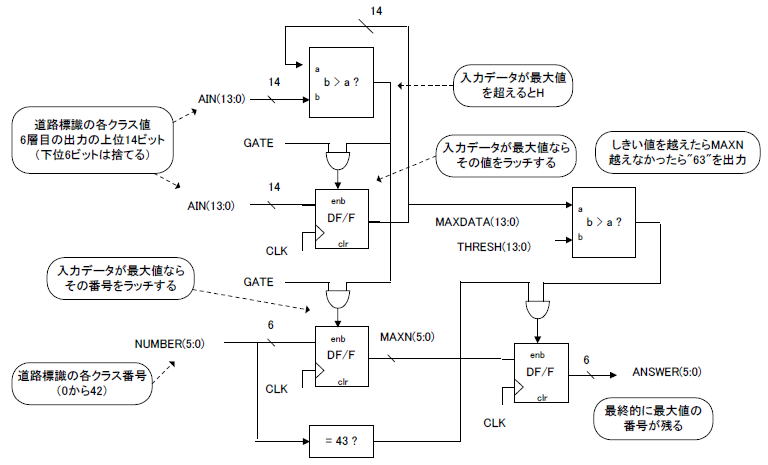

このタイムチャートのmac0, mac1, mac2... mac42は道路標識の43クラスの「点数」になります。そしてこれらの中で最高点のクラスが推論結果となります。図11‐40はその判定を行う回路です。

mac0, mac1, mac2... mac42は判定回路のAINに入力されます(下位6ビットは切り捨てる)。GATEはReluWrNの逆論理になります。

GATEのタイミングでmac0, mac1, mac2... mac42が入ってくるので、逐一最高点と比較し、MAXDATAを更新していきます。

また同じタイミングで最高点のクラス番号MAXNも更新していきます。 |

図11‐40 判定の回路 (judge.vhd)

●各クラス値の最高点を探る

43番目のクラス値と最高点とを比較して終了、そのタイミングでMAXNをラッチしてANSWERとします。またその際、THRESHとMAXDATAを比較し、しきい値を越えたらMAXN(0〜42のいずれか)、越えなかったら”63”を出力します(*1)。

(*1)道路標識がない場合はしきい値を超えないことが多い。”63”なら何もなかったということ |

●回路図をHDL化する

図4‐41にHDLの一部を示します。MAXDATAは推論開始時(START_edge)で0とします。AINがMAXDATAを越えたらb_bt_aが1になり、MAXDATAが更新されます(MAXNも同様)。

MAXDATAがしきい値を超えたらb_bt_100が1になってMAXNがラッチされ、ANSWERに推論結果が出てきます。 |

図4‐41 判定回路のHDL

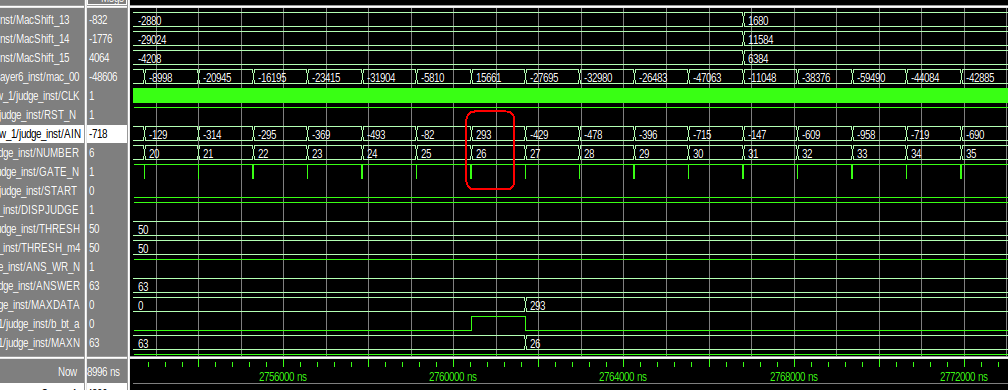

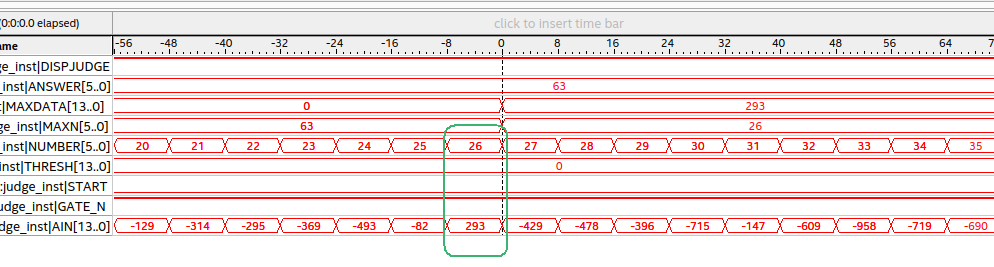

| 判定回路のタイムチャートは省略します(シミュレーションやロジックアナライザで確認、図11‐42、43に一例) |

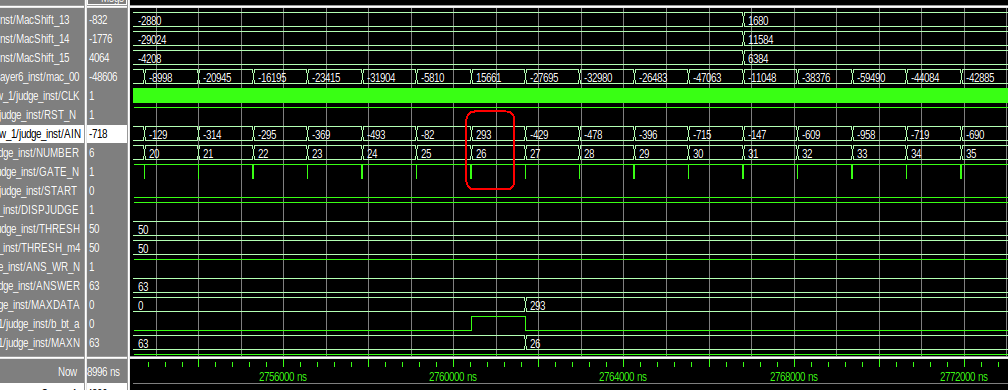

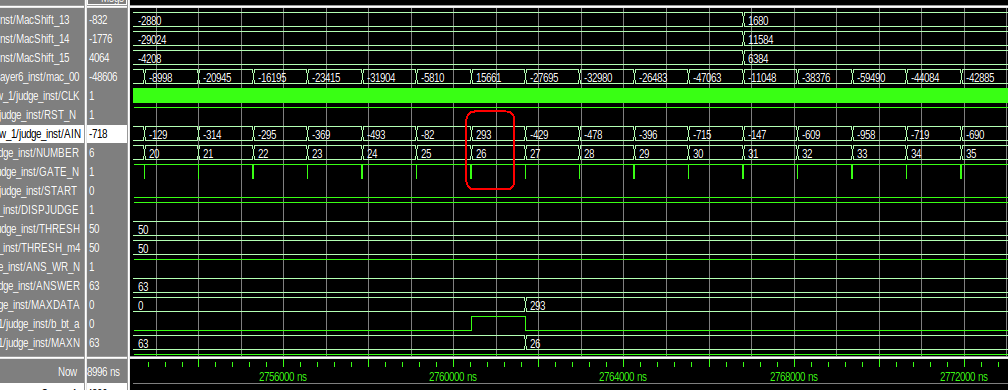

図11‐42 論理シミュレーション。最大値は293、クラス番号は26、MAXDATAに293、MAXNに26

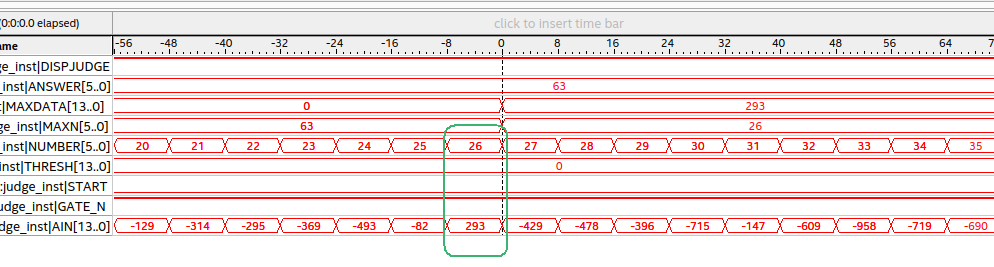

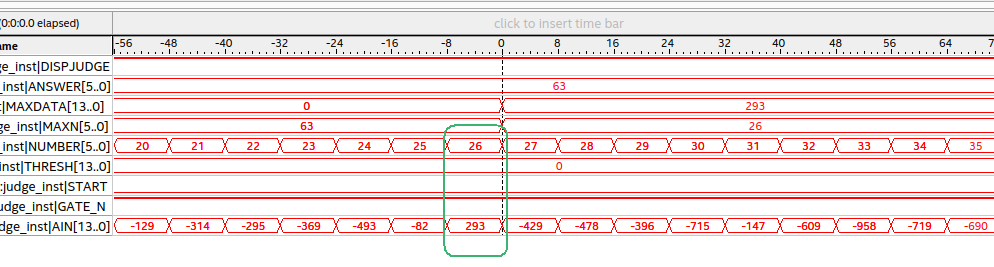

図11‐43 ロジックアナライザ(FPGA内部信号)。最大値は293、クラス番号は26、MAXDATAに293、MAXNに26

最初のページへ

目次へ戻る

|