5‐02 各層間のRAMを考える(続き)

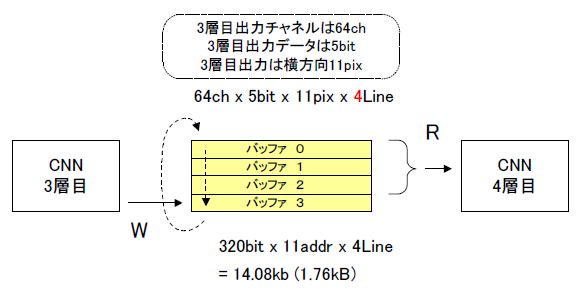

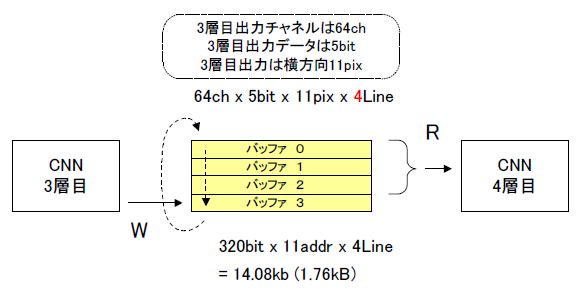

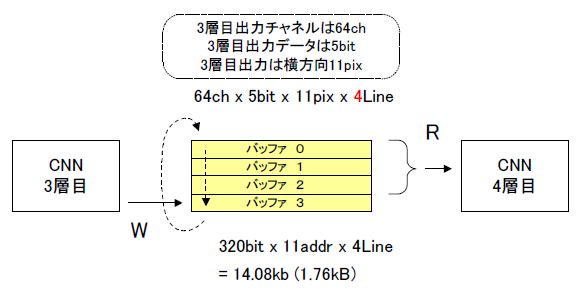

●3層目も同様に4ラインのバッファ

3層目の出力は64ch、データ幅は5ビット、CNN1ブロックの横一ラインは11画素なので、図5‐09のようにビット幅が320、アドレスが11あるバッファが4つあれば済みます。 |

図5-09 3層目の出力が入るメモリ

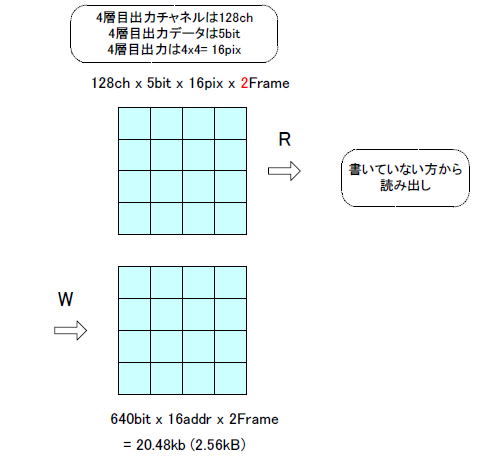

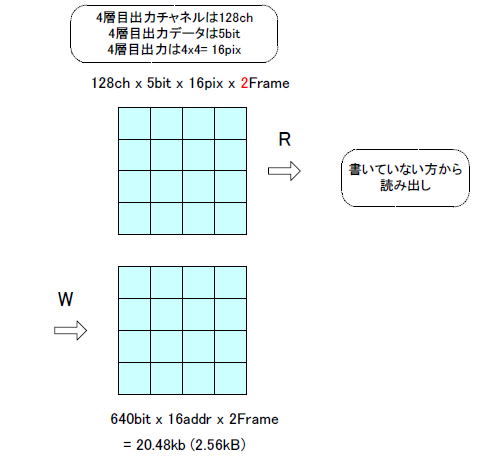

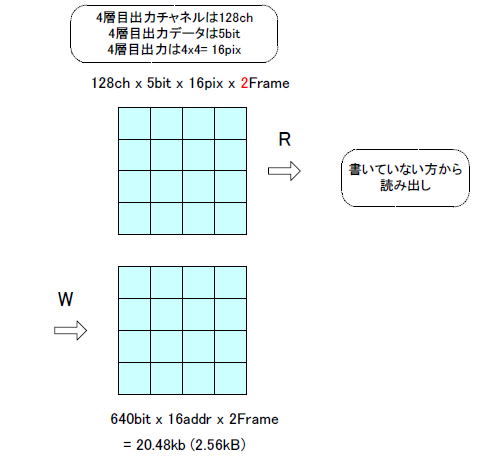

●4層目の出力はフレームバッファ2個に

次はこれの水色の部分、フレームバッファになります(*1)。フレームといっても画面は小さく、図5‐10のように4層目の出力は4×4画素です。チャネル数は128ch、データは5ビットなので、ビット幅が640、アドレスが16あるバッファになります。

フレームバッファの場合は2個必要になります。同図のように書いていない方から読み出します(ピンポンモード)。

(*1)4層目の出力は5層目に入力される。5層目はDense(全結合型)で、読み出し方が変わってくるのでこのようなフレームバッファになる |

図5‐10 4層目と5層目の間に入る(フレームバッファ2個)

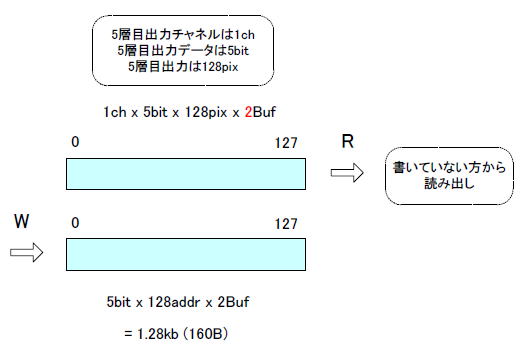

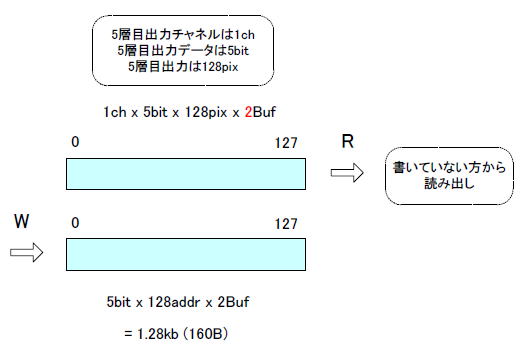

●全結合型なので出力は1ch

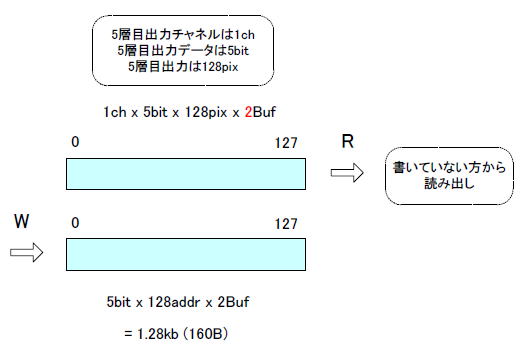

5層目からはDense(全結合型)になります。出力は1ch、データは5ビット、画素数は128なので図5‐11のように、ビット幅が5、アドレスが128あるバッファが2個で済みます。 |

図5‐11 5層目と6層目の間に入る

●4Mbit(500kByte)のSRAMを効率よく使う

FPGAのリソースは限られています。乗算器、レジスタと同様に内部メモリもできるだけ小さく収まるように工夫しましょう。 |

次のページへ

目次へ戻る

|