5‐05 論理シミュレーションの準備

●やみくもにFPGAに実装してもまず動かない

HDLコーディングが一通り終わったら論理シミュレーションを行い、HDLが所望の動作をしているかを確認します。ある程度の規模の回路になるとシミュレーションは必須になります。FPGAに実装する前に必ず行いましょう。

●Mentor Graphics社が提供する論理シミュレータの無償版を使う

論理シミュレータはQuesta Intel Starter FPGA Edition、またはModelSim Intel(Altera) Starter Edition(どちらも無償版)を使います。Intel社のサイトからダウンロードできます(*1)

(*1)QuestaはQuartus Prime Lite Editon、ModelSimはQuartus II Web Editionに付属している。ダウンロード・インストール法は若干違うが、使用法は基本的に同じ |

●プロジェクトを新規作成するには

論理シミュレーションのプロジェクトを丸ごとコピーしても、ディレクトリ構成、OSやQuesta/Modelsimのバージョンの違い等でうまく動かないことが多いと思います。したがってプロジェクトを一から作る方法を説明します。

まず、このアーカイブを解凍すると(*2)、tb_VideoProcフォルダが現れます。適当なフォルダ(例えばGTSRB/SIM以下)にコピーします。以下にその際のディレクトリ構成。

(*2)解凍にはパスワードが必要です(これまたはこれのセミナ参加者のみに通知)

| GTSRB |

|

|

|

|

|

|

| |-- |

|

SIM |

|

|

|

|

|

|

|-- |

|

tb_VideoProc |

|

|

|

|

|

|

|-- |

design |

回路本体(実際にFPGAに実装するファイルがある) |

|

|

|

|

|-- |

sim |

環境ファイル(シミュレーション用、FPGAには実装しない) |

|

|

|

|

|-- |

run.do |

シム実行用スクリプト |

|

|

|

|

|-- |

wave.do |

波形表示用スクリプト |

|

|

|

|

|-- |

initmem.txt |

SDRAM初期化データ |

|

●プロジェクトの新規作成

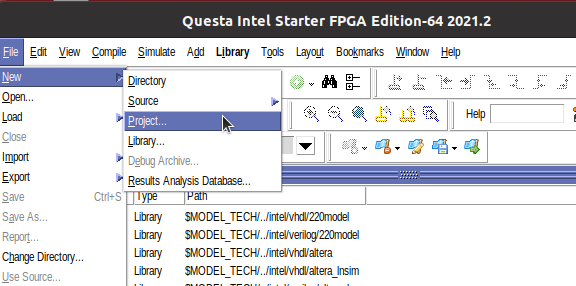

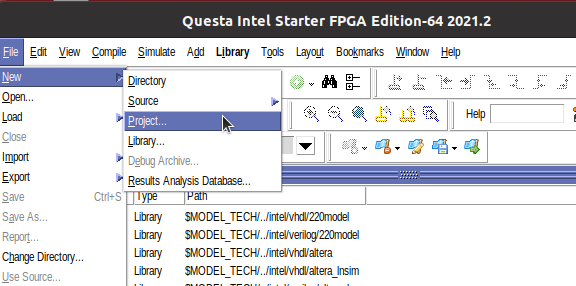

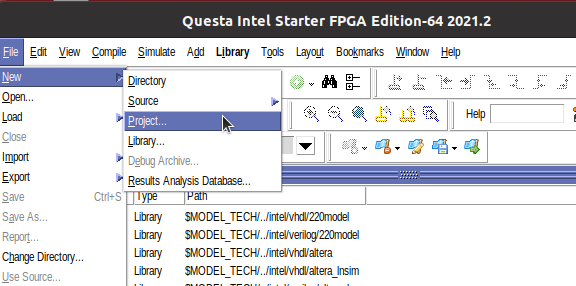

Questa/ModelSimをスタートする。

メニューのFile→New→Projectを選択。 |

図5‐40

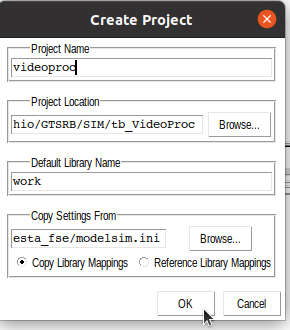

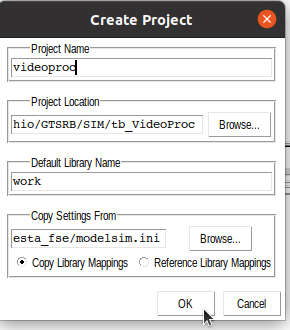

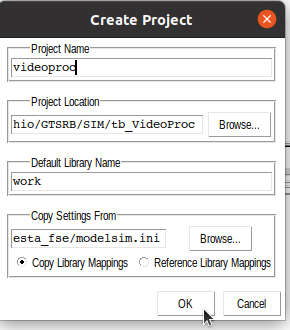

| プロジェクト名をvideoprocとし、Project Locationでtb_VideoProcディレクトリを選択してOKをクリック。 |

図5‐41

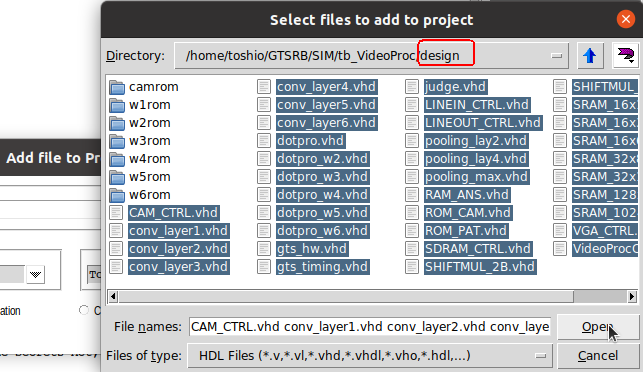

| Add Existing Filesをクリックし、Browseをクリック。 |

図5-42

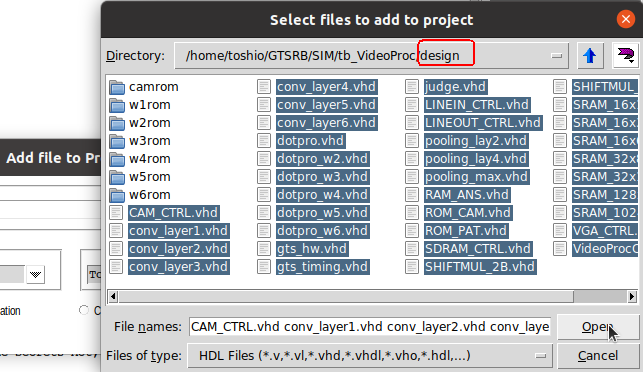

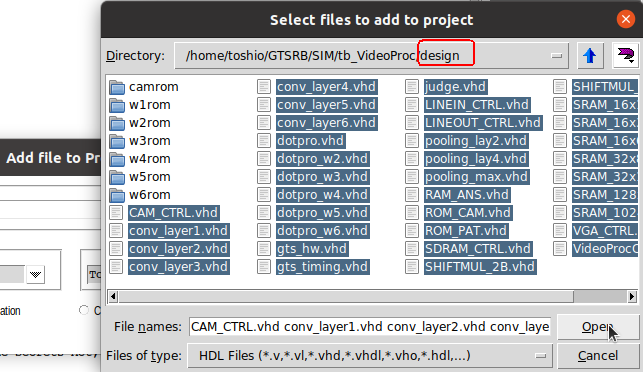

| tb_VideoProcの下、designフォルダ内の全VHDLファイルを選択してOpen。 |

図5‐43

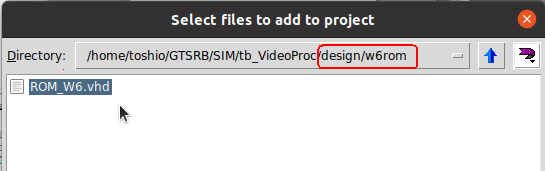

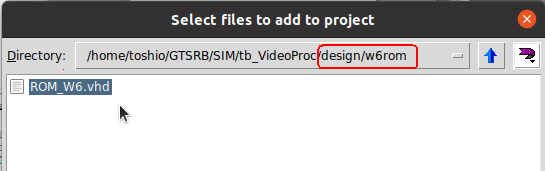

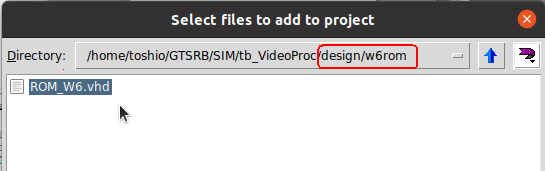

| またdesignの下、camrom, w1rom〜w6romフォルダ内の全VHDLファイルも選択してOpenします。以上は回路本体(実際にFPGAに書き込むファイル)になります。 |

図5‐44

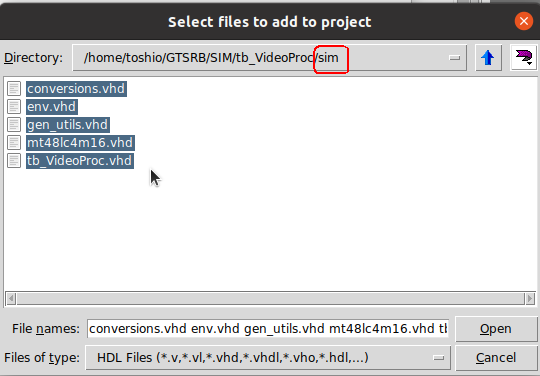

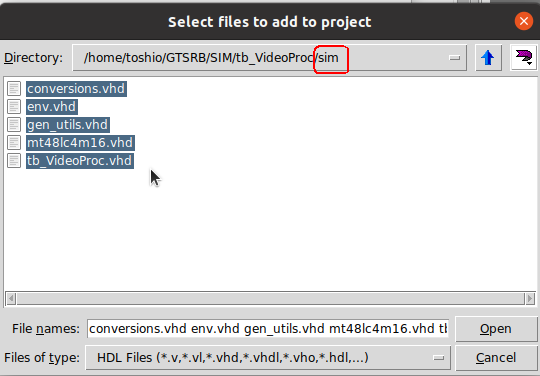

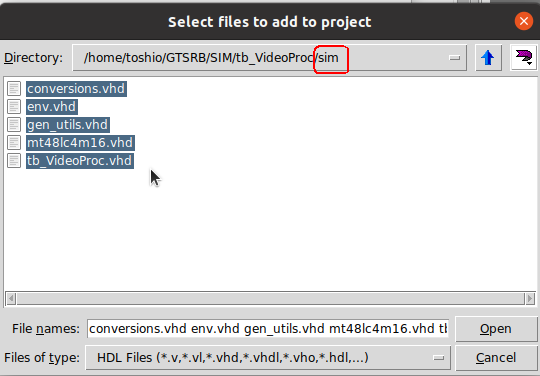

| さらにtb_VideoProcの下、simフォルダ内の全VHDLファイルも選択します。これらは環境ファイル(シミュレーションだけに使用するファイル)になります。 |

図5‐45

次のページへ

目次へ戻る

|