5乚05丂榑棟僔儈儏儗乕僔儑儞偺弨旛乮懕偒乯

仠僐儞僷僀儖仺幚峴

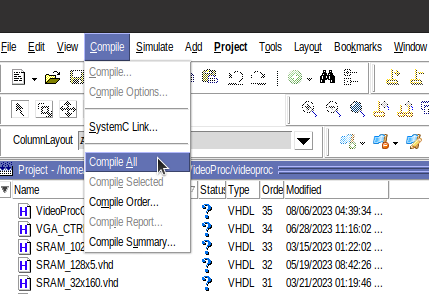

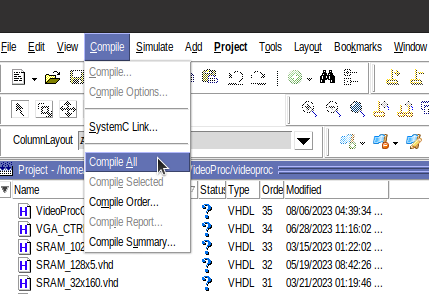

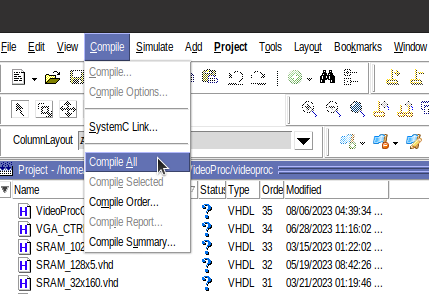

丂儊僯儏乕偺Compile仺Compile All傪慖戰丅 |

恾5-48

| 丂慡僼傽僀儖偑僐儞僷僀儖偝傟丄Transcript偺榞撪偵no errors偲弌偰偒偨傜惉岟丅 |

恾5乚49

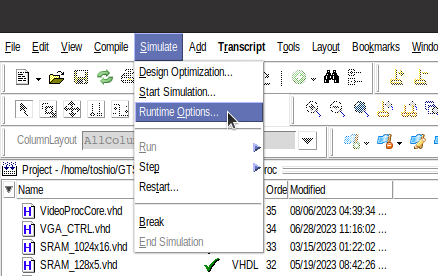

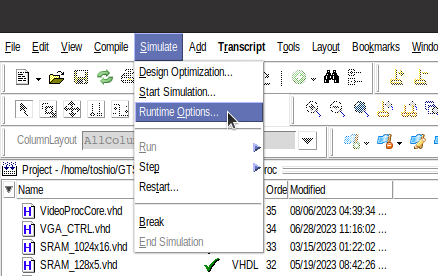

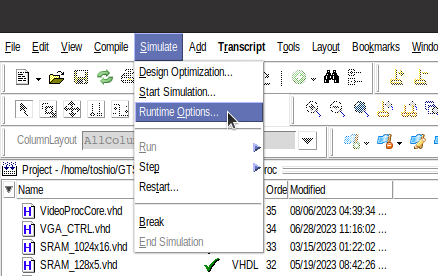

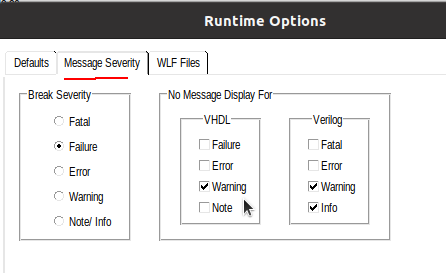

| 丂偙偙偱儊僯儏乕偐傜Simulate -> Runtime Option傪僋儕僢僋 |

恾5乚50

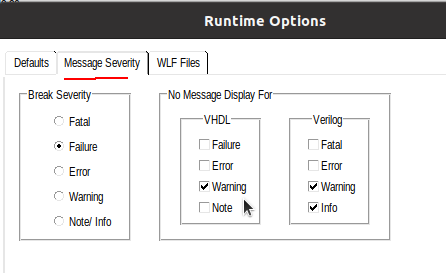

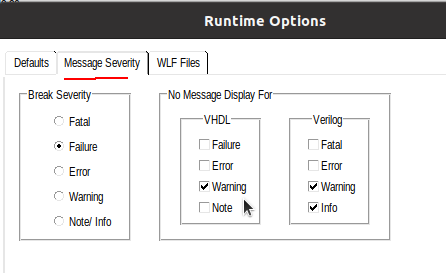

| 丂Message Severity僞僽偱VHDL偺Warning傪僠僃僢僋丅偙傟偱Warning偑弌側偔側傝丄僔儈儏儗乕僔儑儞偑懍偔側傝傑偡丅 |

恾5乚51

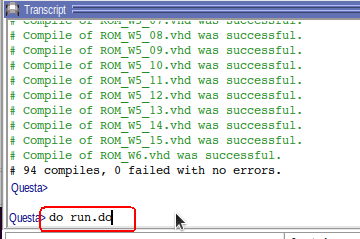

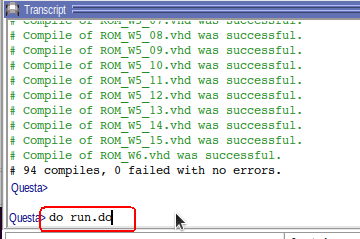

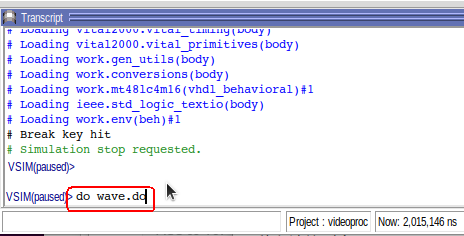

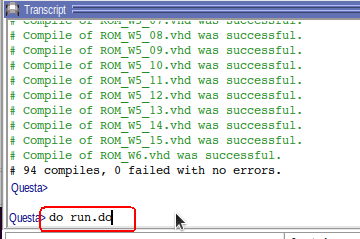

| 丂Transcript偐傜do run.do偲僞僀僾偟偰儕僞乕儞丅 |

恾5乚52

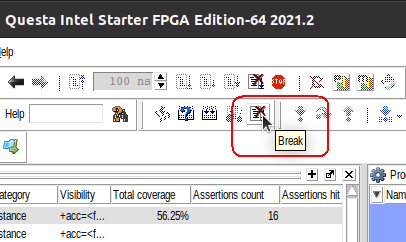

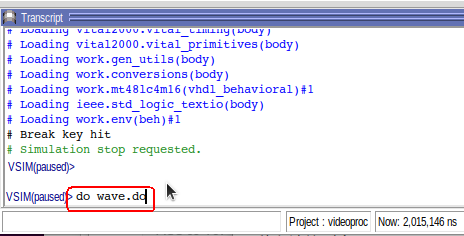

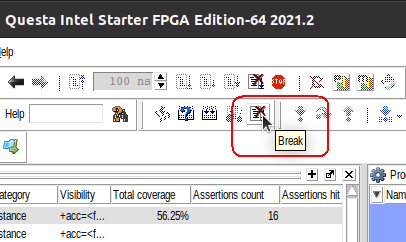

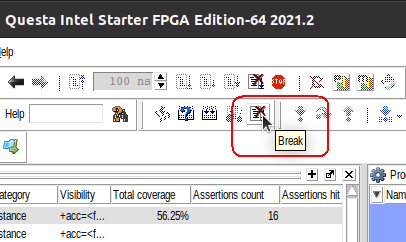

| 丂僔儈儏儗乕僔儑儞偑僗僞乕僩偟傑偡丅巭傔偨偄偲偒偼Break儃僞儞傪僋儕僢僋偟傑偡丅 |

恾5乚53

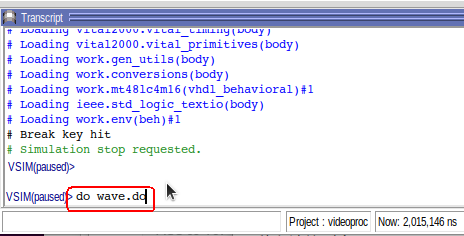

丂2ms掱搙偱僔儈儏儗乕僔儑儞傪巭傔乮仏侾乯丄do wave.do偲僞僀僾偟傑偡丅

乮仏侾乯Questa亄Linux側傜30暘掱搙丄ModelSim亄Windows側傜2帪娫掱搙偐偐傞偐傕偟傟傑偣傫乮儅僔儞偺惈擻偵傛傞丅巹偺娐嫬偱偦偺傛偆側姶偠乯

|

恾5乚54

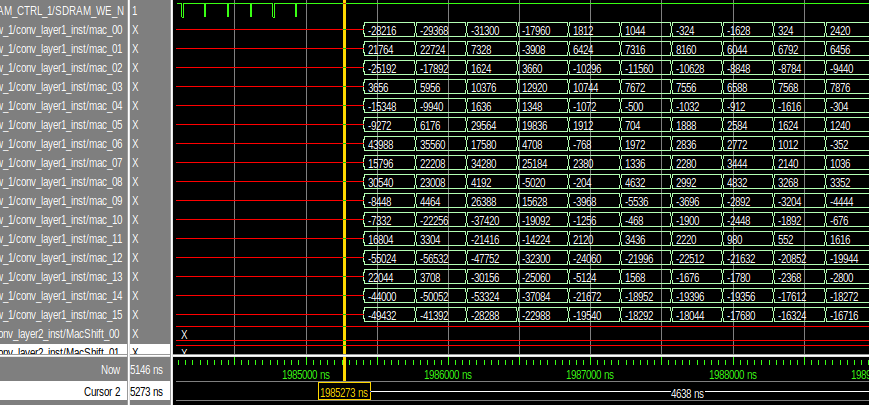

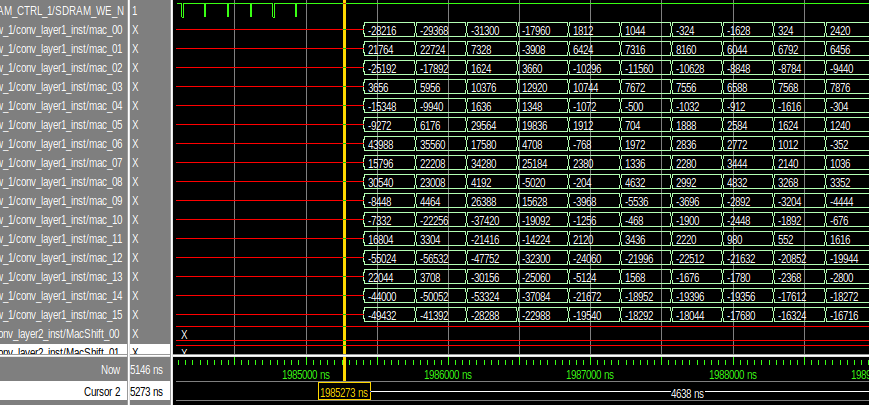

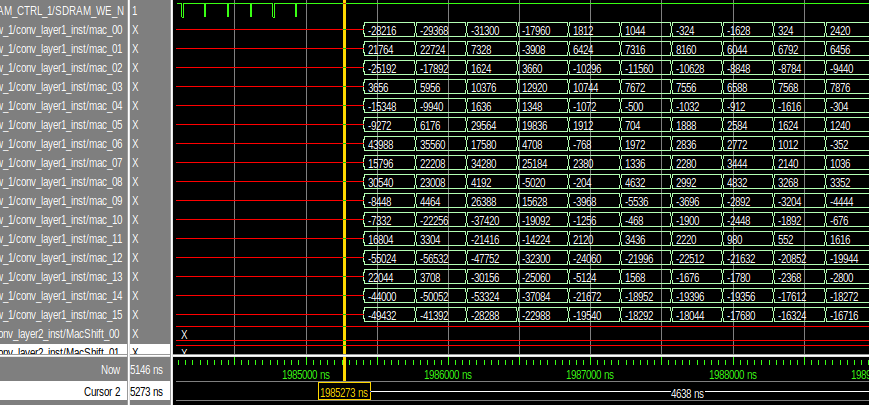

| 丂WAVE僂僀儞僪僂偵攇宍偑昞帵偝傟傑偡丅壓恾偱偼gts_hw/conv_layer1乮CNN1憌栚乯偺mac_00乣15乮愊榓墘嶼婍16屄乯偺弌椡傪尒偰偄傑偡丅 |

恾5乚55

| 丂SDRAM弶婜壔僼傽僀儖乮initmem.txt)偵傛傝懍傗偐偵CNN悇榑傪巒傔傞偙偲偑偱偒傑偡丅偦偺僼傽僀儖偺惗惉朄偼偙偙傪嶲徠丅 |

嵟弶偺儁乕僕傊

栚師傊栠傞

|