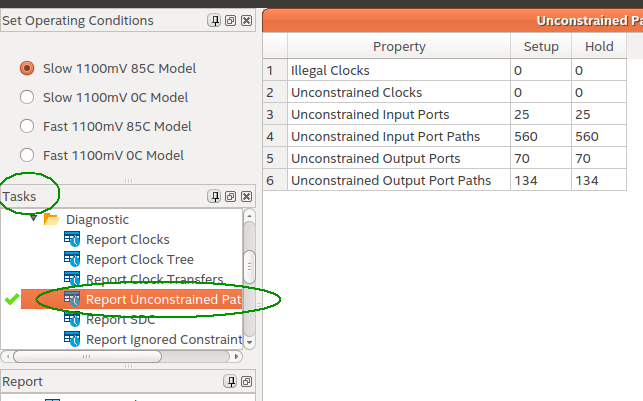

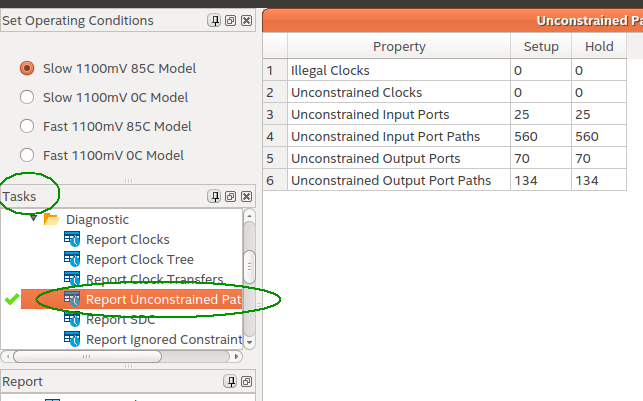

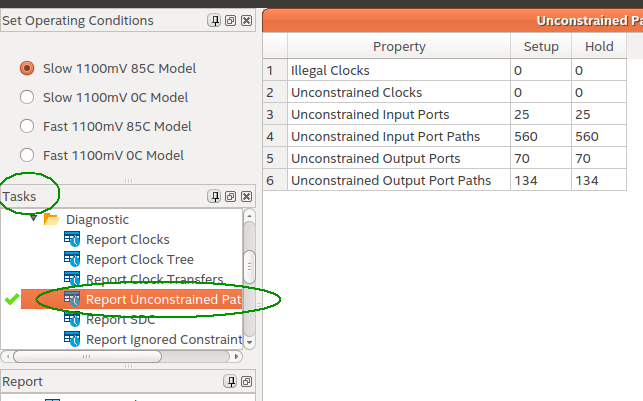

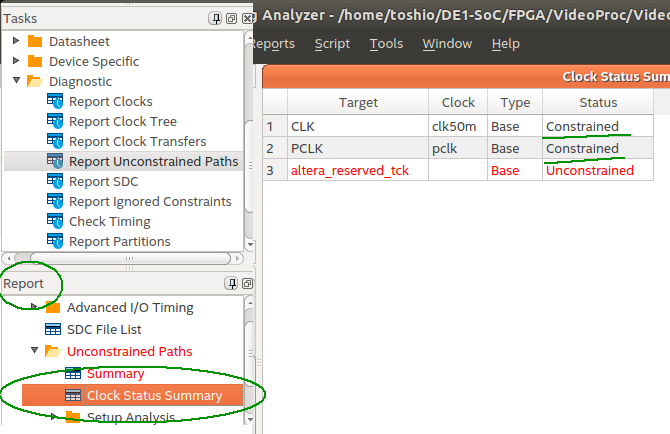

| 下図のようにTasks枠のReports -> Diagnostic -> Report Unconstraint

Pathをダブルクリック。 |

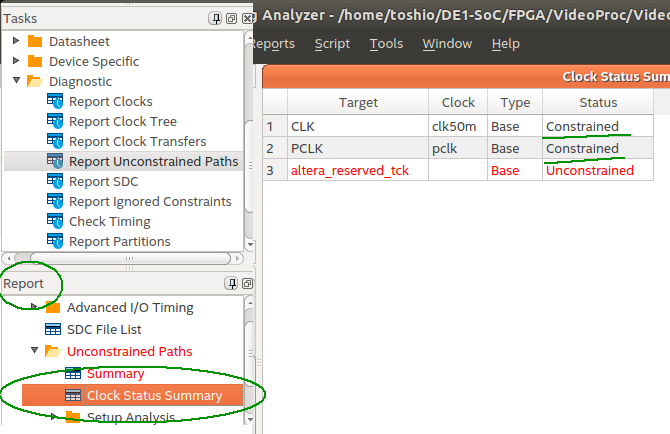

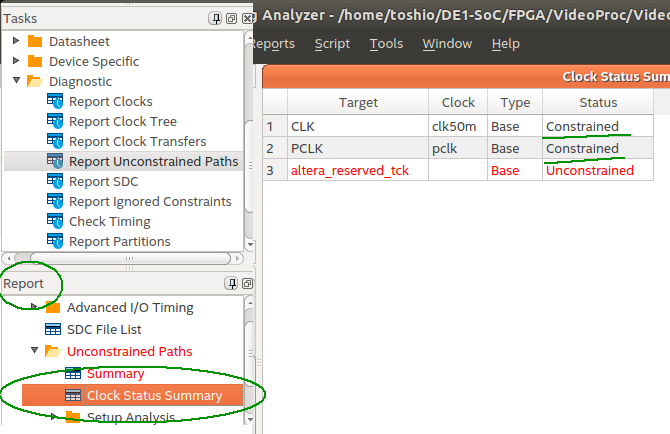

下図のようにReport枠のUnconstrained paths -> Clock status summaryをダブルクリック。

CLKとPCLKがConstrainedになっているのを確認。(*2)

(*2)Unconstrainedの信号はコンフィグレーション用と思われる。特にコンストレインの必要はない |

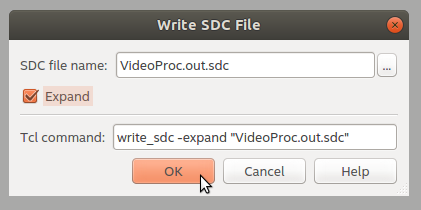

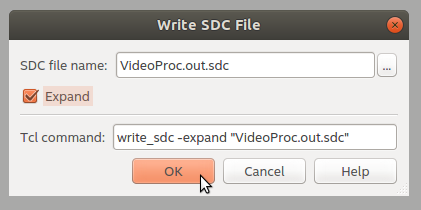

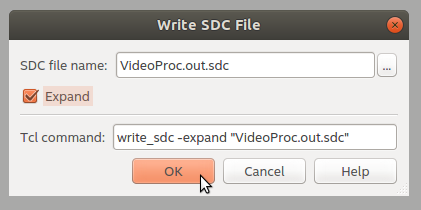

| Timing Analyzerを終了します。「SDCをWriteしますか?」と聞かれるのでYes。 |

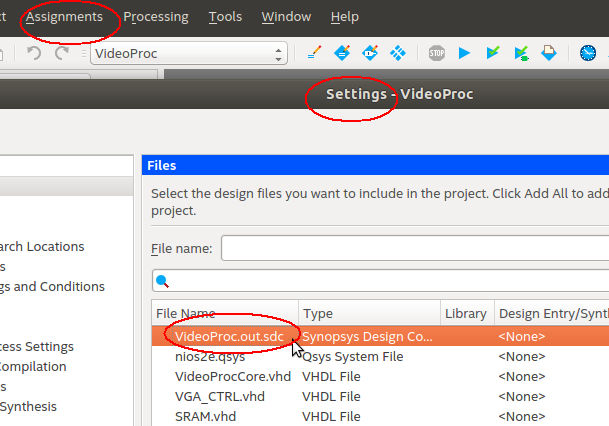

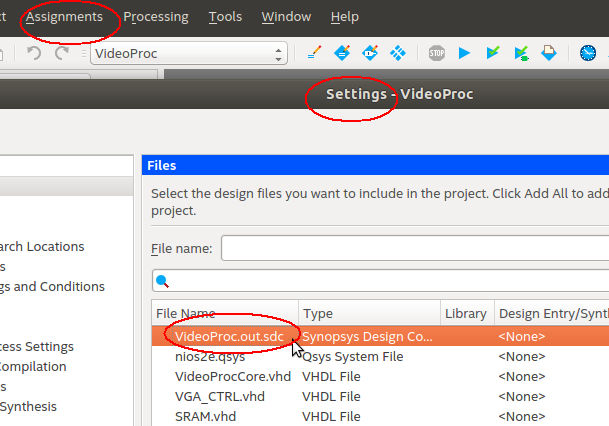

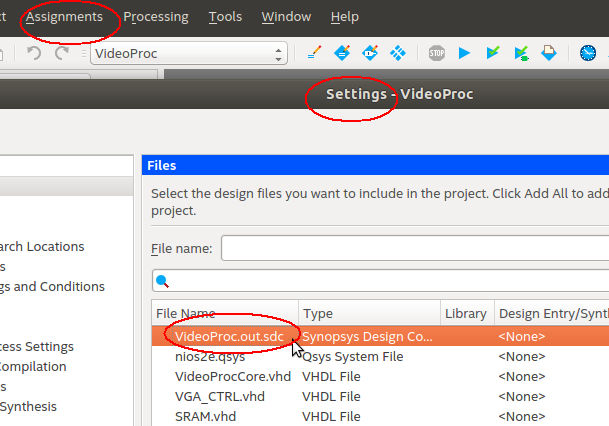

Quartusに戻り、Assignment -> Settingsを選択します。

下図のようにFile nameからVideoProc.out.sdcを選択してAddします。 |

その後コンパイルし、FPGAに書き込みます。

書き込んだ回路は「CLKが50MHzである」、「PCLKが25MHzである」ことを前提に配置配線されています。以上のようにタイミング・コンストレインはQuartusに入力クロック周波数などのタイミング制約を伝える作業です(*3)。

(*3)たいていの場合タイミング・コンストレインは入力クロックのみ行えば事足りる。 |

最初のページへ

目次へ戻る

|