このアーカイブを解凍して適当なディレクトリにコピーした後、適当なディレクトリでFftRtl_1024.vhdを開きましょう。 このアーカイブを解凍して適当なディレクトリにコピーした後、適当なディレクトリでFftRtl_1024.vhdを開きましょう。

これがFFTの最上位モジュールです。ENTITYの部分に入出力ピンが定義されています。仕様や回路図に関してはここを参照してください。 これがFFTの最上位モジュールです。ENTITYの部分に入出力ピンが定義されています。仕様や回路図に関してはここを参照してください。

VHDLファイルは全部で14個ありますが、その中でFFT本体は以下に示す9個からなります。 VHDLファイルは全部で14個ありますが、その中でFFT本体は以下に示す9個からなります。

以下の5個は「環境ファイル」と呼ばれるもので、FFT本体にテスト信号を注入するためのものです。 以下の5個は「環境ファイル」と呼ばれるもので、FFT本体にテスト信号を注入するためのものです。

環境ファイルの最上位にあるtb_fft.vhdはテストベンチと呼ばれ、FFT本体と信号発生回路(datas.vhd,

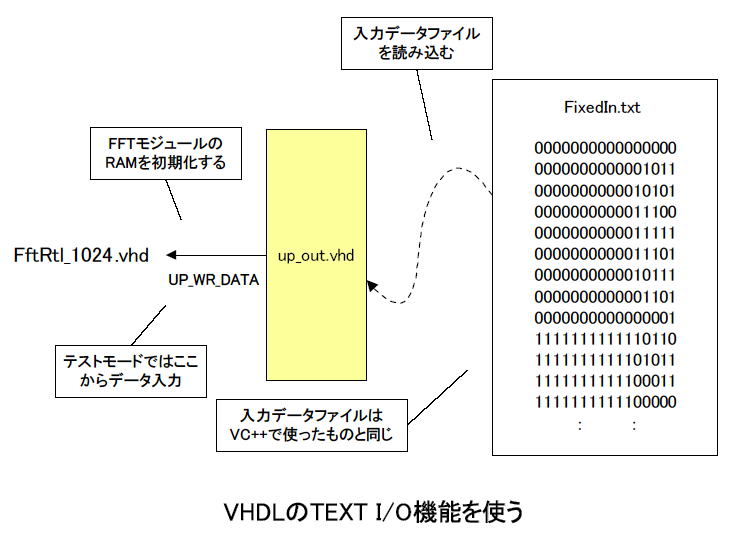

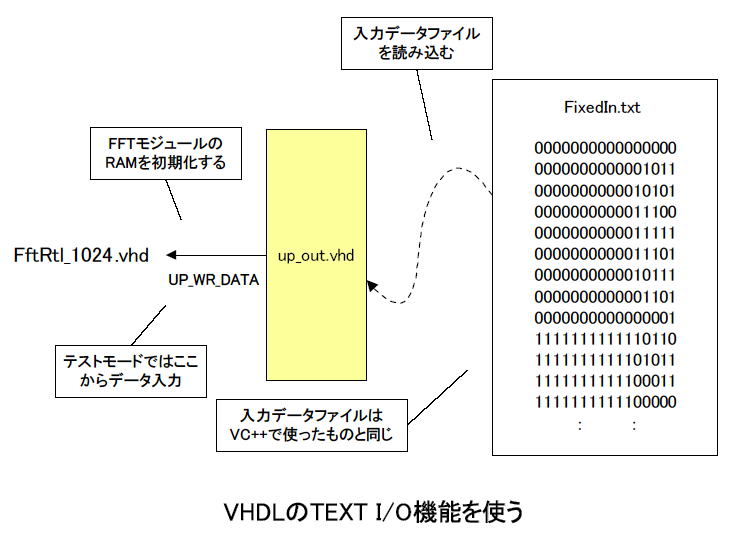

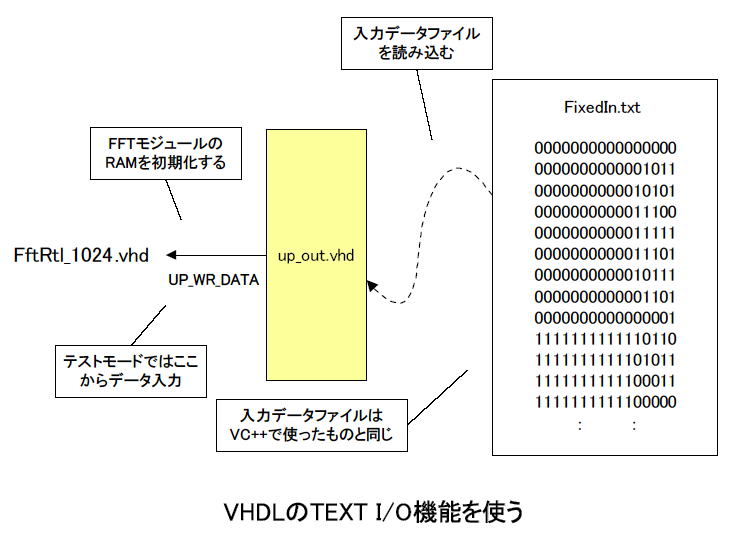

clks.vhd, up_out.vhd)をつないでいます。clks.vhdは水晶発振子をエミュレートするものでFFT本体にクロックを供給し、datas.vhdはA/DコンバータをエミュレートするものでFFT本体にシリアルデータを供給します(ノーマルモード)。up_out.vhdはマイコンをエミュレートするもので、FFT本体にキャプチャ(A/Dからのデータ取り込み)開始やFFT開始のトリガをアサートします。 環境ファイルの最上位にあるtb_fft.vhdはテストベンチと呼ばれ、FFT本体と信号発生回路(datas.vhd,

clks.vhd, up_out.vhd)をつないでいます。clks.vhdは水晶発振子をエミュレートするものでFFT本体にクロックを供給し、datas.vhdはA/DコンバータをエミュレートするものでFFT本体にシリアルデータを供給します(ノーマルモード)。up_out.vhdはマイコンをエミュレートするもので、FFT本体にキャプチャ(A/Dからのデータ取り込み)開始やFFT開始のトリガをアサートします。

また、up_out.vhdはFixedIn.txtを読み込んでFFTの入力データとする機能も持ちます(テストモード)。FixedIn.txtは前回の「C言語を固定小数点化する」で使用したものと同じものです。 また、up_out.vhdはFixedIn.txtを読み込んでFFTの入力データとする機能も持ちます(テストモード)。FixedIn.txtは前回の「C言語を固定小数点化する」で使用したものと同じものです。

また「C言語を固定小数点化する」ではFixedTri.txtを読み込んで三角関数としていました。 また「C言語を固定小数点化する」ではFixedTri.txtを読み込んで三角関数としていました。

ここでTriRom.vhdを開いてみましょう。このようにVC++で使用されたものと同じものがVHDLに張り付けられています。 ここでTriRom.vhdを開いてみましょう。このようにVC++で使用されたものと同じものがVHDLに張り付けられています。

したがって、もしFFTが正しくVHDL化されていれば、前回のVC++で得られたFFT結果と、今回のVHDLシミュレーションで得られるFFT結果がまったく同じものになるはずです。 したがって、もしFFTが正しくVHDL化されていれば、前回のVC++で得られたFFT結果と、今回のVHDLシミュレーションで得られるFFT結果がまったく同じものになるはずです。

|