3-03 層間の画素データを5ビットにする

●FPGAに入りきるようビット幅を削減する

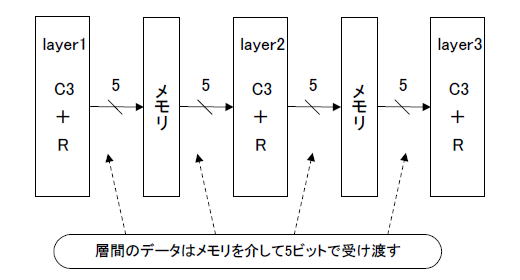

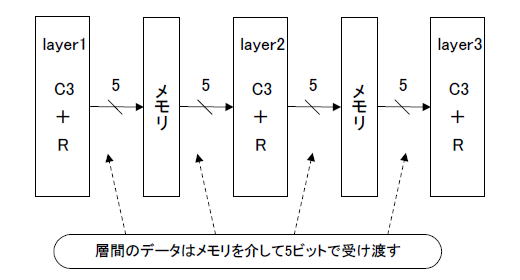

ハードウエアにおいて、vgg1層目の出力は図3‐06のようにメモリを介して2層目に入力されます。また2層目の出力も同様にメモリを介して3層目に入力されます。

SSDは画素数やチャネル数が多いため、メモリを節約するためにビット幅を最低限にする必要があります。ただしあまり少なすぎると認識率が悪くなるため、同図のようにビット幅は5ビットとします。 |

図3‐06 メモリ(FPGA内部RAM)を介して受け渡す

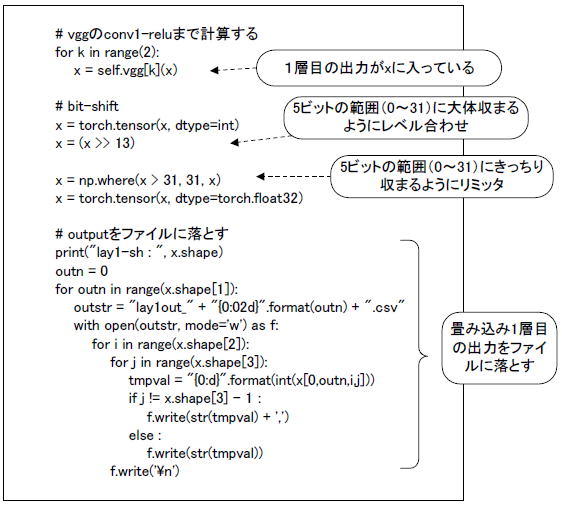

●乗算の後はビットシフトとリミッタ

元々小数だった重み係数が整数化されているので乗算結果は大きくなります。さらに図3‐06のようにビット幅5という制限があるので、画素データは0〜31の範囲にある必要があります(*1)。したがってリスト3-08のように「レベル合わせ」や「リミッタ」を施します。

(*1)vgg層はReLU関数を持つので負の値はない |

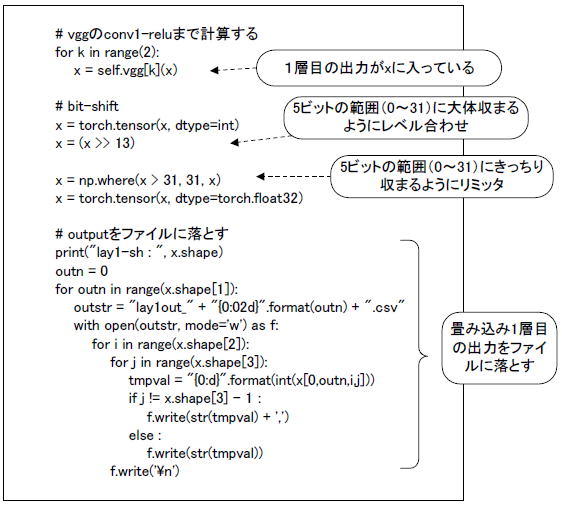

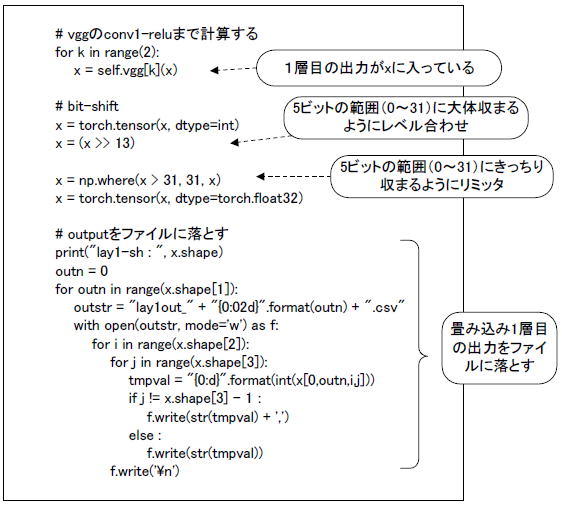

リスト3-08 乗算後速やかにビットシフトして値を小さくする

リスト3‐08は1層目の出力で、bit-shiftの部分が(x >> 13)になっています。

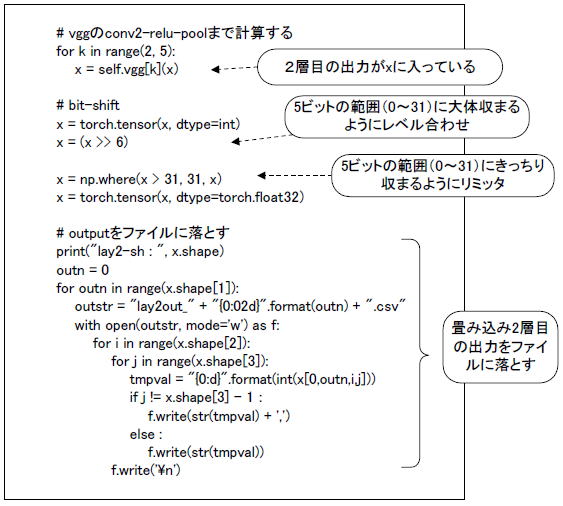

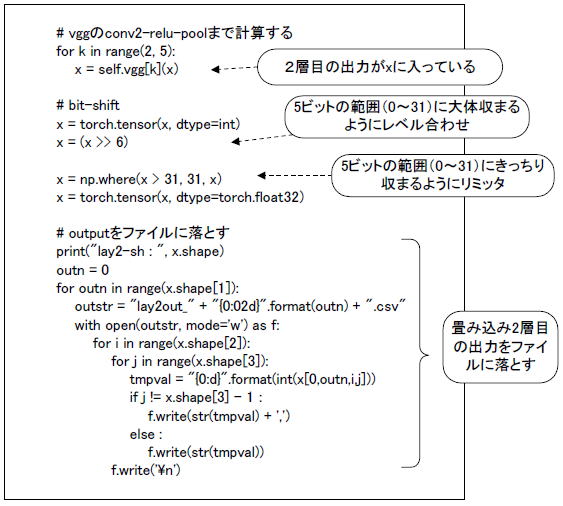

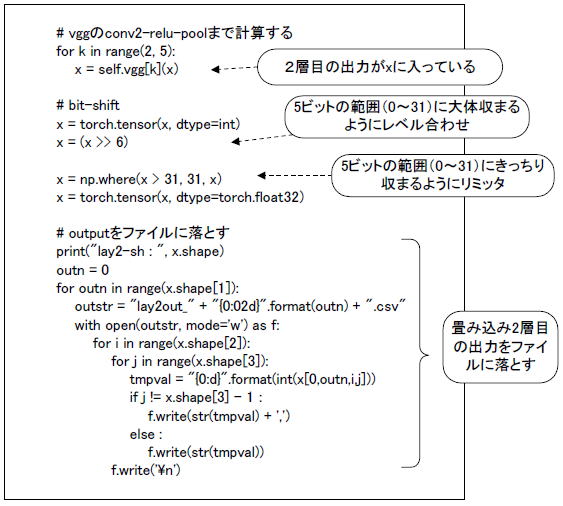

それに対しリスト3‐09は2層目の出力で、bit-shiftの部分が(x >> 6)になっています。

このように各層、出力のボリュームが違うので、0〜31の範囲におさまるよう適宜ビットシフト量を調整します。(*2)

(*2)各層、試行錯誤的に調整した |

リスト3-09 この層は6ビットシフトすると大体0〜31に収まる

| このようなビットシフトとリミッタを全層(vgg1〜15、extra1〜8、conf2〜6)の出力に施します。 |

目次へ戻る

|