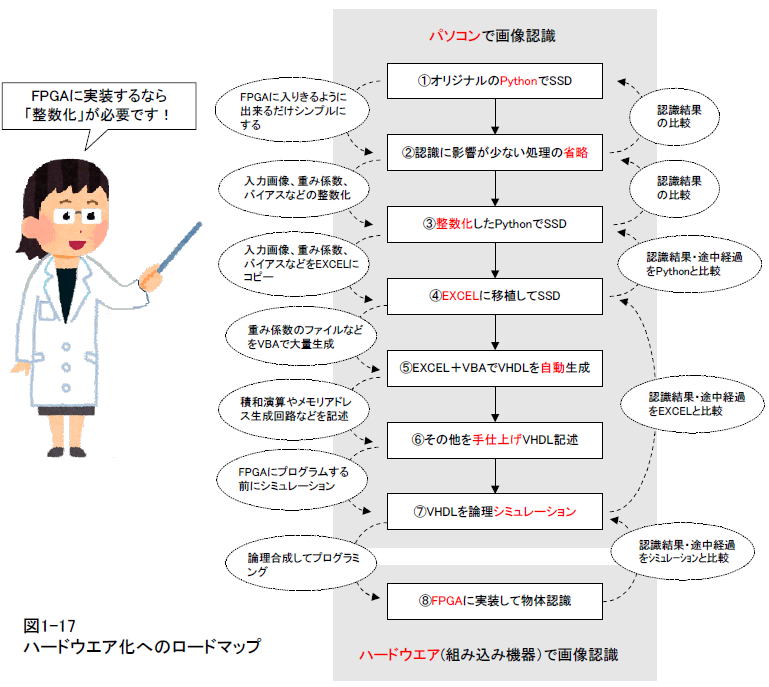

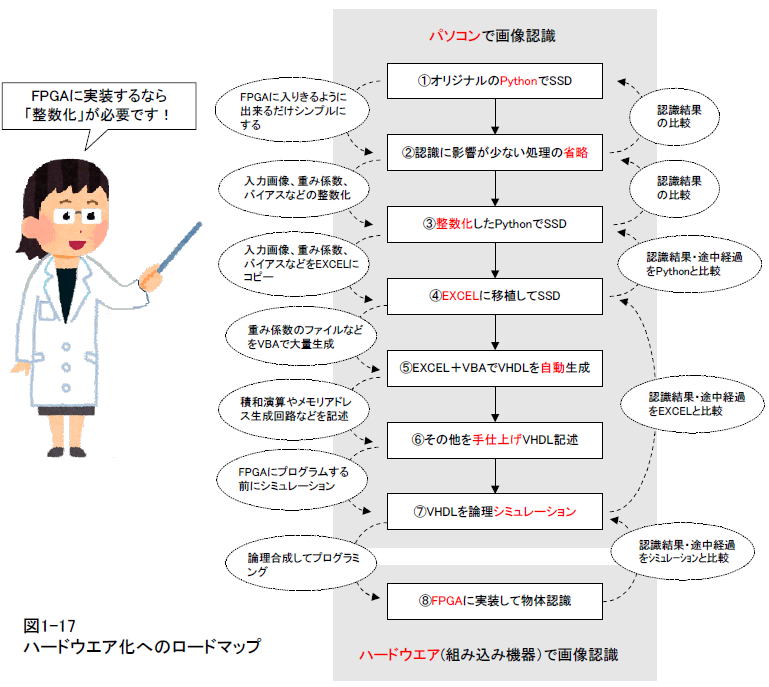

本企画では図1-17のようにディープラーニングのハードウエア化を進めます。一番上の①からスタート、一番下の⑧がゴールです。

①オリジナルのPythonでSSD

まずはPythonで書かれたプログラムを普通に実行します。当然ながらプログラム内の変数(画素値など)や定数(重み係数など)は小数になっています。その認識結果は当該書籍と同じになります。

②認識に影響が少ない処理の省略

SSDはとても複雑なアルゴリズムなので、そのままハードウエア化するとFPGAに入りきらない可能性が大です。したがってPythonの段階で削れる処理は削っていきます。その認識結果をオリジナルと比べ、許容範囲であることを確認します。

③整数化したPythonでSSD

パソコンで計算するぶんには小数でよいのですが、FPGAでは小数の演算は行えません(*1)。したがってPythonの段階から整数化して実行します。整数化によって認識率は低下しますが、それが許容範囲か確認します。

テスト画像1枚分のデータ、重みの係数などをファイルに落とします。これらはすべて整数になっています。

また計算の途中経過(各層の出力など)もファイルに落とします。

(*1)FPU(Floating Point Unit)を内蔵していれば行えるが、そのようなFPGAは少数派である |