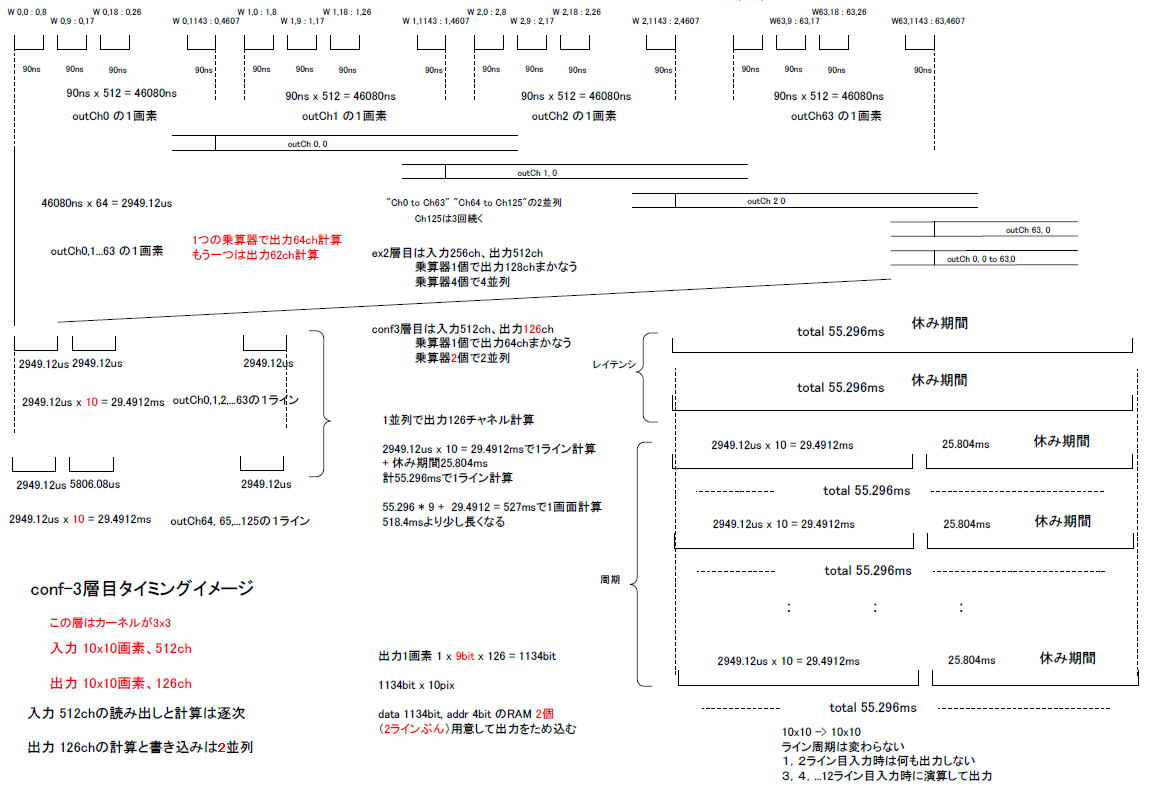

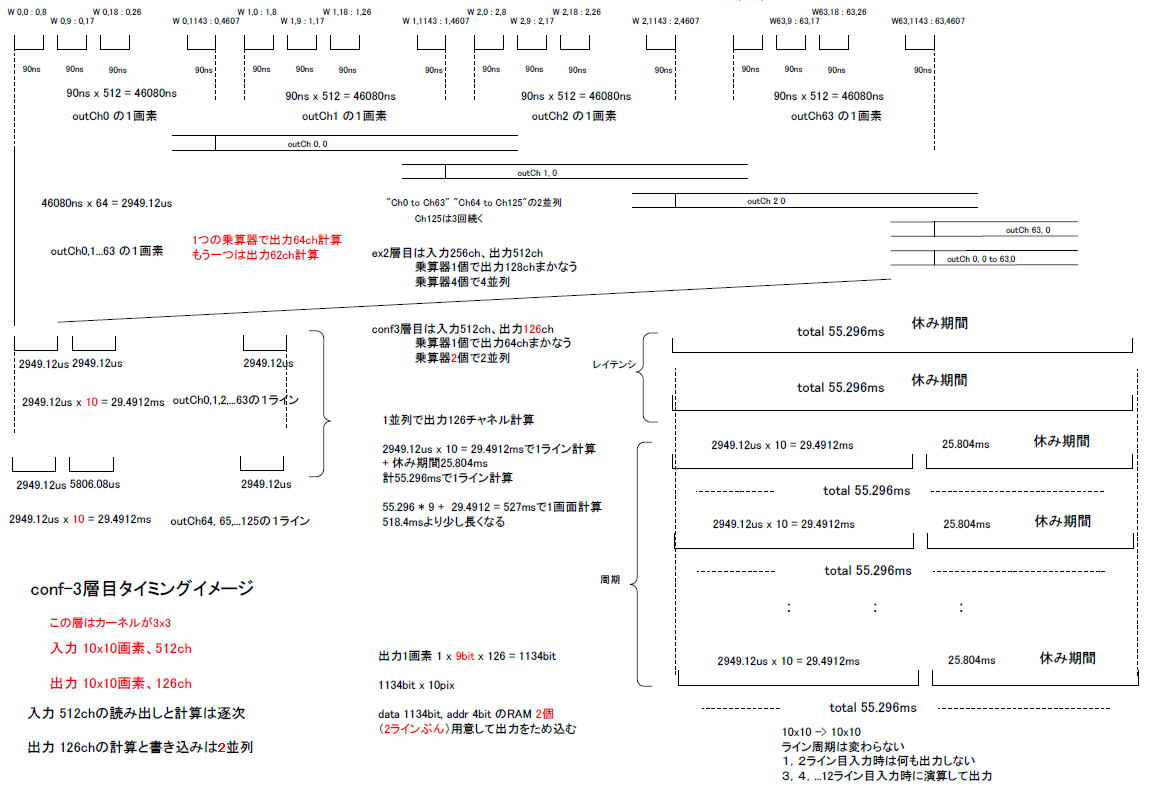

●64ch×2並列で出力126ch

図10-10の上段はoutCh0,1,2,...63を計算するようすです。これら出力64chは1個の乗算器で「逐次的に」計算されます。したがって1画素の計算にかかる期間は90ns

x 512 x 64 = 2949.12usになります。

1ライン10画素なので2949.12us x 10 = 29.4912msで1ライン計算しますが、同図右にあるように「休み期間」が25ms程度あるので計55.296msで1ライン、1画面19ラインなので55.296ms

* 9 + 29.4912 = 527msで1画面の計算が終わります。

「outCh64 to outCh125(これは62ch)」も1つの乗算器で計算されます。乗算器(ビットシフト型)が2個並列で64chづつ計算して出力は64

+ 62 = 126chになります(入力は512ch)。 |