10-02 conf-4, 5, 6層目のVHDL化(続き)

●conf-6層目は3x3

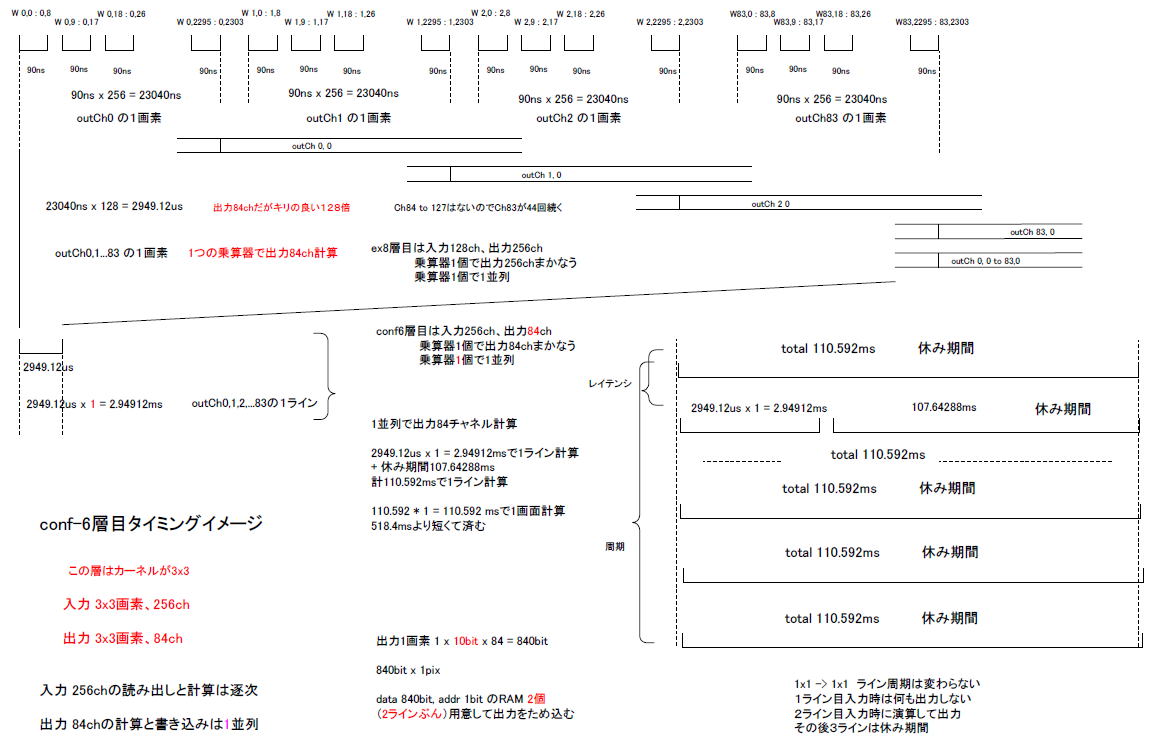

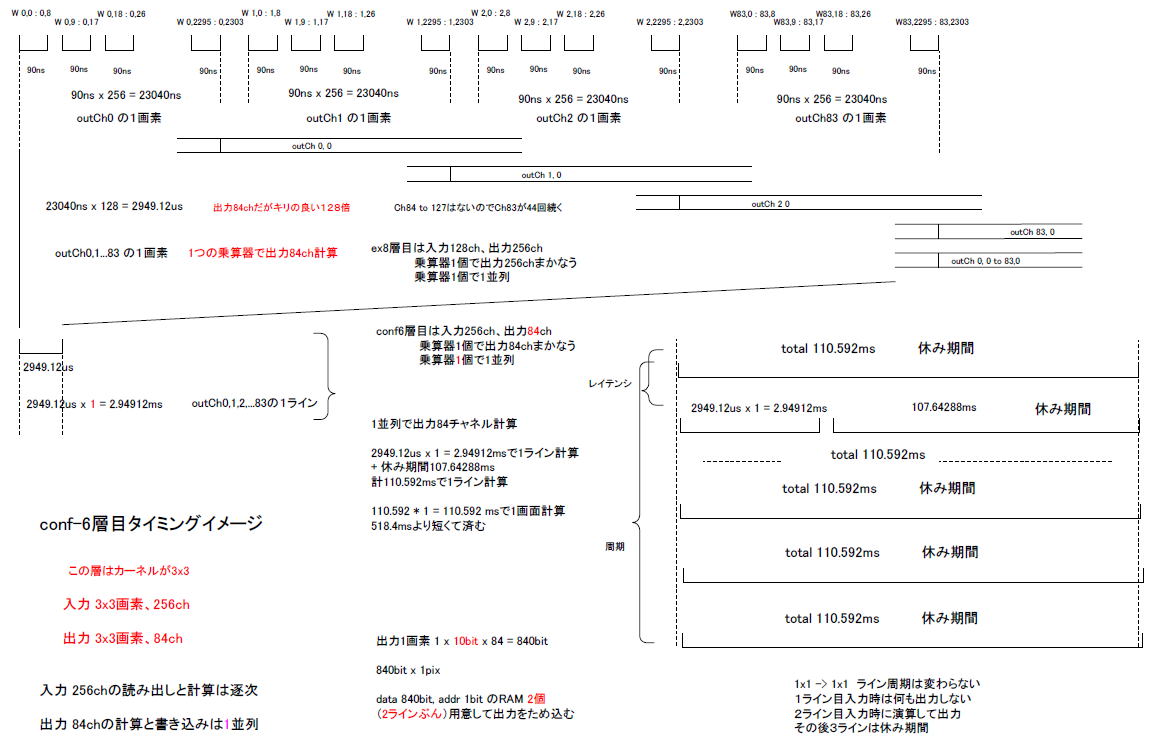

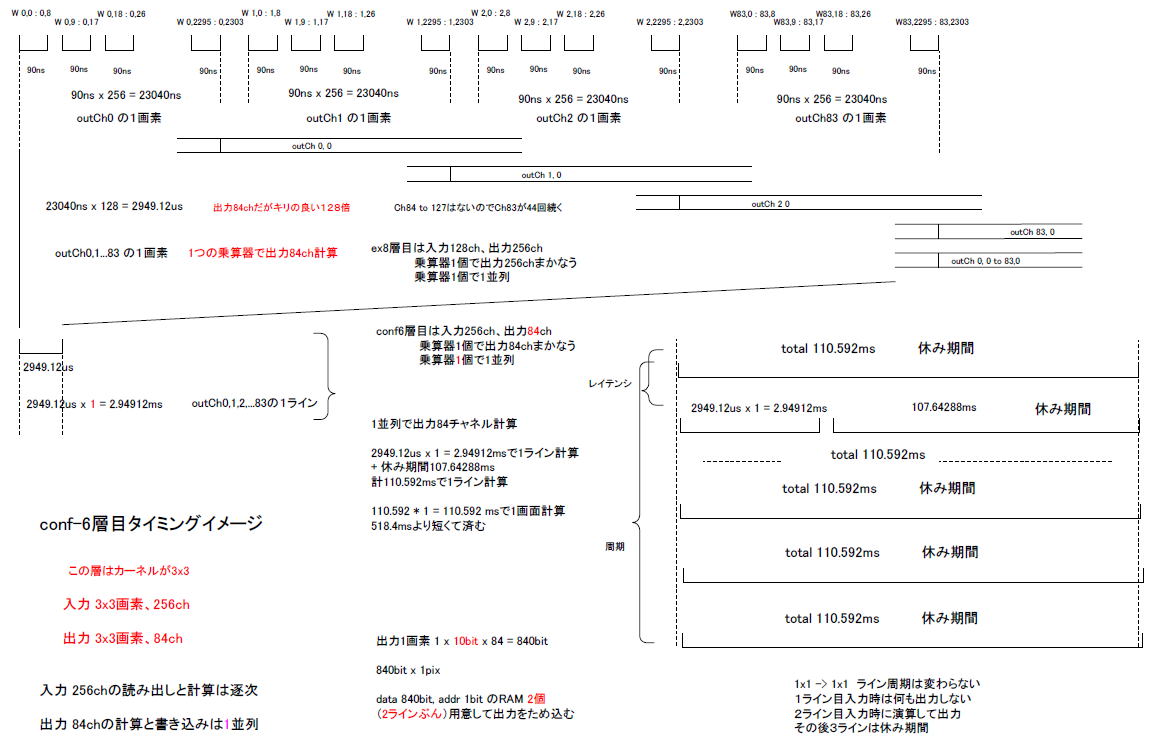

extras-8層目の出力はconf-6層目に入力されます。図10-40にそのタイミングのイメージを示します。

conf-6層目の入力は256ch、出力は84chになります。カーネルは3x3、この層では1つの乗算器で出力を84ch、1並列で計84ch計算します。 |

図10-40 conf-6層目のタイミングのイメージ

●1並列で出力84ch計算

図10-40の上段はoutCh0,1,2,...83を計算するようすです。これら出力84chは1個の乗算器で「逐次的に」計算されます。したがって1画素の計算にかかる期間は90ns x 256 x 128 = 2949.12usになります(84ではなくキリの良い128)。

1ライン1画素なので 2949.12us x 1 = 2.94912msで1ライン計算しますが、同図右にあるように「休み期間」が107ms程度あるので計110.592msで1ライン、1画面1ラインなので110.592msで1画面の計算が終わります。 |

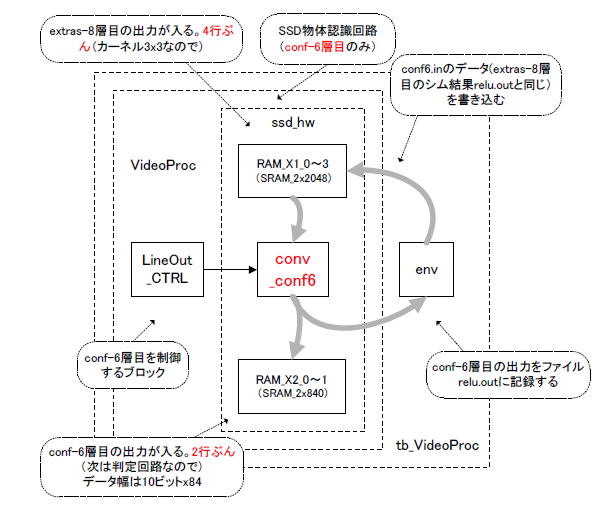

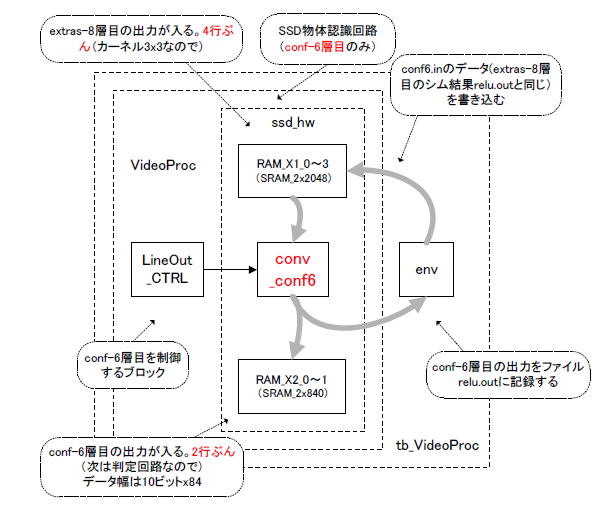

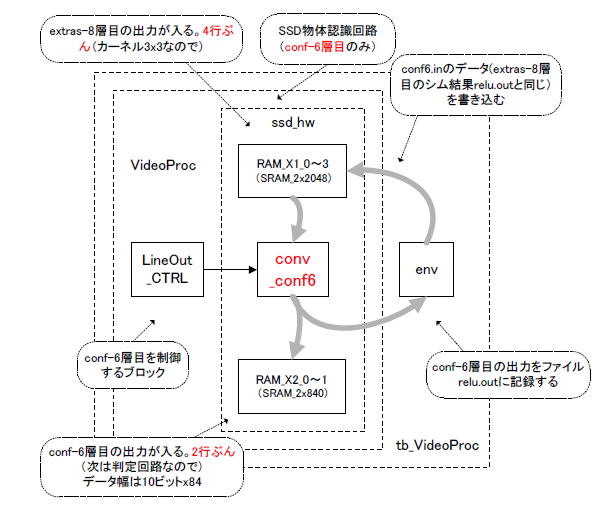

●extras-8層目の出力がconf-6層目の入力になる

extras-8層目のシミュレーション結果relu.outの名前を変えてconf6.inとし、それがconf-6層目の入力になります。図10-41のようにRAM_X1_0〜3(入力バッファ、4ラインぶん、カーネルが3x3なので)にconf6.inの内容が書き込まれます。

conv_conf6は入力バッファからの画像を処理してRAM_X2_0〜1(出力バッファ、2ラインぶん、次は判定回路なので2つで十分)に書き込みます。1ライン3画素なのでアドレスは4、出力84chなのでデータ幅は10bit x 84 = 840bitになります(この層は1画素10ビット)。 |

図10-41 conf-6層目のブロック図

次のページへ

目次へ戻る |