9-01 extras-1, 2層目のVHDL化(続き)

●stride=2 ゆえに画素数が減る

extras-2層目の畳み込みは少し違い、パディングは1、そしてストライドが2になります。

図9-10のように枠を1画素分拡げ、3x3のカーネルを2画素ぶん横にに動かしながら積和演算を行います。縦方向も同様に2ラインぶん動かすので、その結果出力は10x10画素になります。 |

図9-10 プーリングなしでもこうすれば画素数が減る

●画素やラインの飛ばし方

図9-11ではbaseaddrにcount3を加算して入力バッファのアドレスを生成してます。baseaddrはカーネルの位置を表すもので、0,

2, 4, 6,...と2づつ増えており、これは横方向のストライドが2ということです。

縦方向はバッファ選択のベースになる信号を2づつ増やしていきます。これらによってstride

= 2が達成できます。 |

図9-11 baseaddrが読み出しアドレスのベースになる

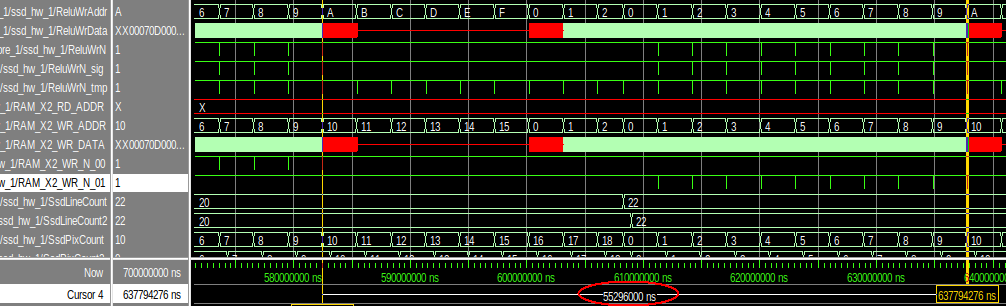

●画素数とライン数が減ったので計算周期が長くなる

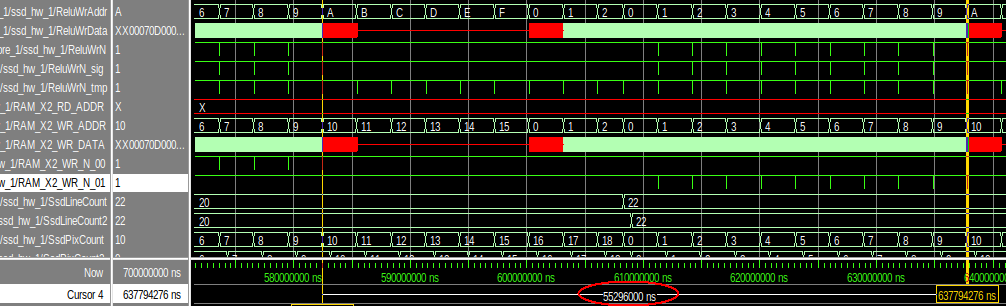

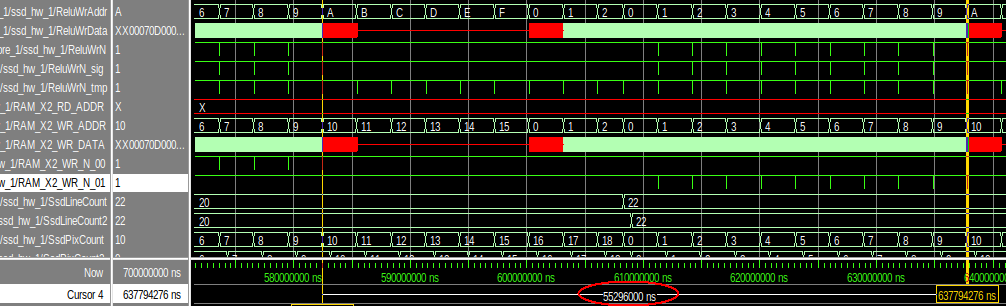

1ライン書きこむ周期は図9-12のように55.296msになります。これを10ラインぶん繰り返して1画面終了します。 |

図9-12 1ライン演算して書き込むようす

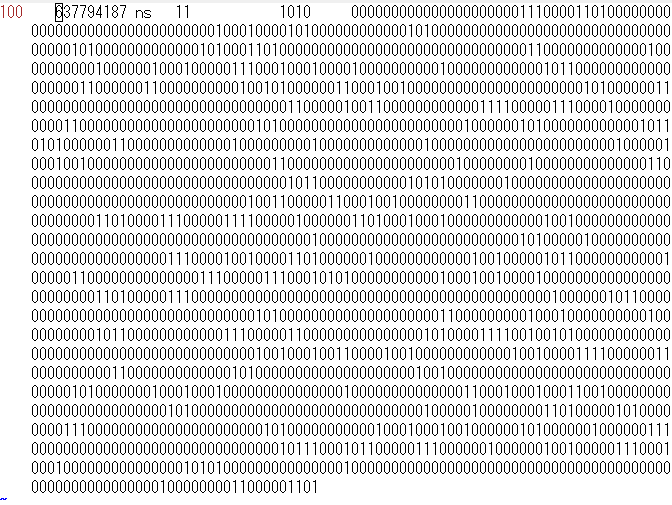

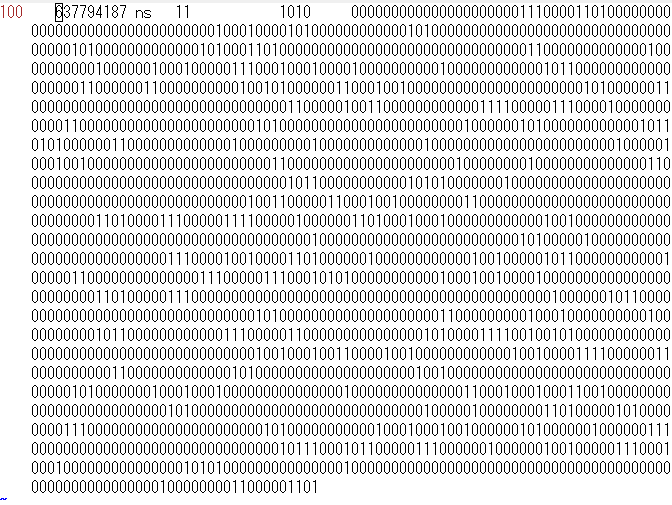

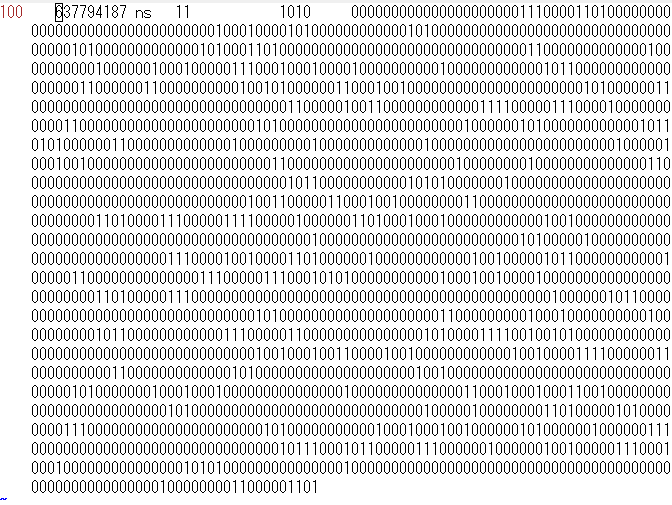

●relu.outに出力が書かれている

extras-2層目も出力はテキストファイルに落とされます(図9-13。10×10画素なので1画面で100行、また出力は512チャネルなのでビット幅は

8bit x 512= 4096bit になります。これをVBAで512個のCSVファイルに分割してPythonの結果と比較します。 |

図9-13 10x10で100行、8ビットx512chで各行4096ビット

●バッチファイルでまとめて比較する

CSVファイルが512個もあるので、前層までと同様にバッチファイルによって比較し、全てのチャネルがピタリ一致することを確認します。 |

最初のページへ

目次へ戻る |