8-03 vgg-3, 4層目のVHDL化(続き)

●3層目のシミュレーション用プロジェクト

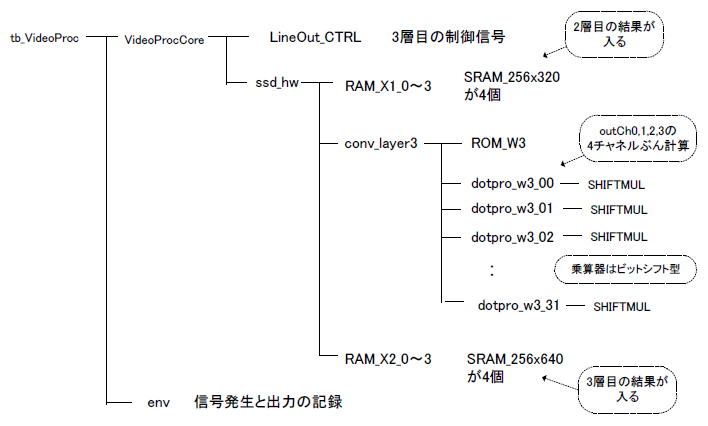

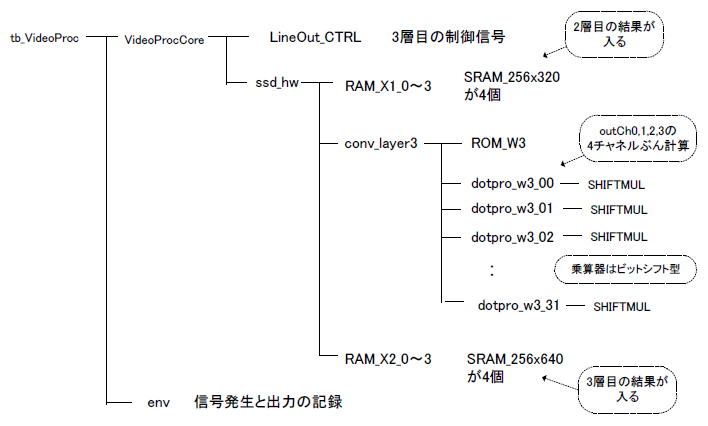

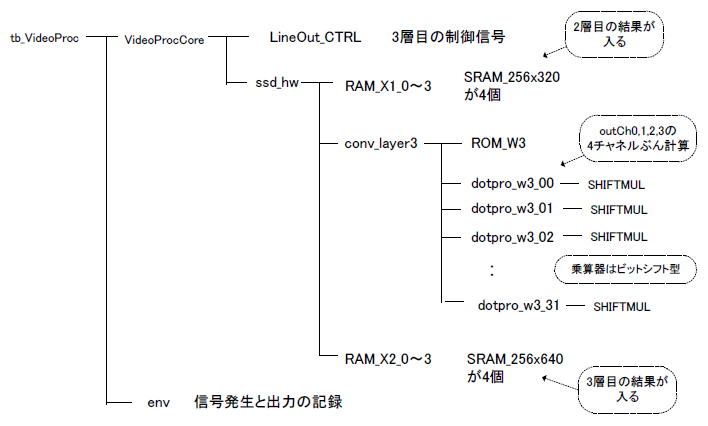

vgg-3層目のModelSim(シミュレータ)プロジェクトのアーカイブを解凍すると図8‐44のような構成になっています。入力は64チャネル、出力は128チャネルですが積和演算器(dotpro_w3_xx)は32個です。すなわち1個の積和演算器で出力4チャネルを受け持ちます。例えばdotpro_w3_00はoutCh0,1,2,3の計算を行います。 |

図8-44 vgg-3層目のツリー構造

●Relu_00は4chぶん多重化されているので分離する

図8‐45はModelSimシミュレーションのようすです。積和演算→ビット削減→ReLuの結果、Relu_00〜31という信号になります。そこまでは32個の信号ですが、図8‐45ではRelu_00を5.76us毎にデマルチプレクスして4つの信号reg_00_0〜3に分解しています。

このように処理するので、出力の1画素を計算するのにかかる時間は 90ns x 64 x 4 = 23.04us になります。 |

図8‐45 Relu_00の値0, 5, 2, 1がそれぞれreg_00_0, 1, 2, 3に渡される

●3層目の出力がバッファに書かれるようす(env内)

そして1ラインは150画素なので 23.04us x 150 = 3.456ms で1ライン計算します。図8‐46のReluWrSelは出力ラインバッファ(4個)の切り替え信号で、3.456ms周期で切り替わっています。 |

図8‐46 出力1ライン計算に3.456ms

●relu.outに出力が書かれている

3層目も出力はテキストファイルに落とされます。図8‐47はrelu.outの最後の部分、150×150画素なので1画面で22500行、また出力は128チャネルなのでビット幅は 5bit x 128 = 640bit になります。これをPythonの結果と比較します。 |

図8-47 relu.outに3層目の結果が書かれる

次のページへ

目次へ戻る |