8-03丂vgg-3, 4憌栚偺VHDL壔乮懕偒乯

仠4憌栚偺僔儈儏儗乕僔儑儞梡僾儘僕僃僋僩

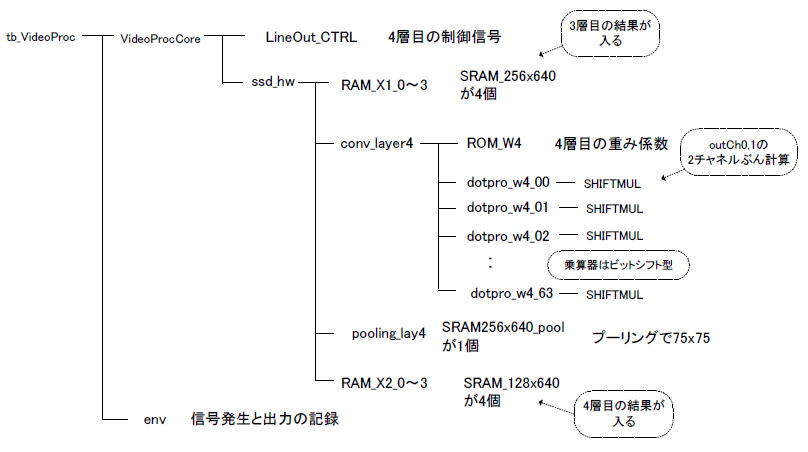

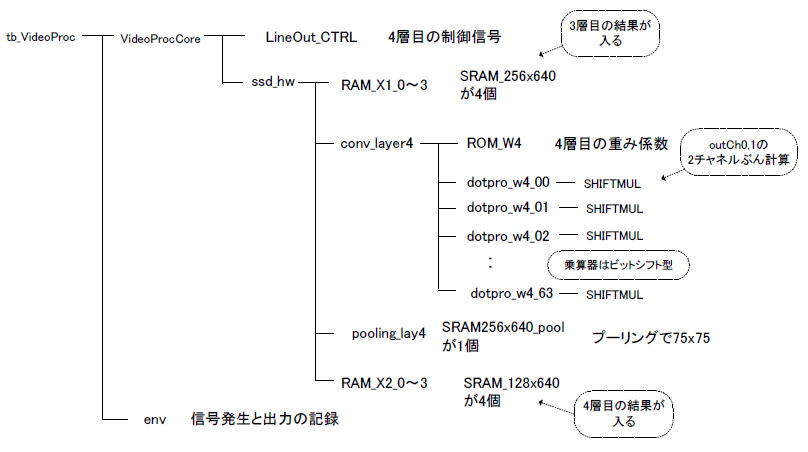

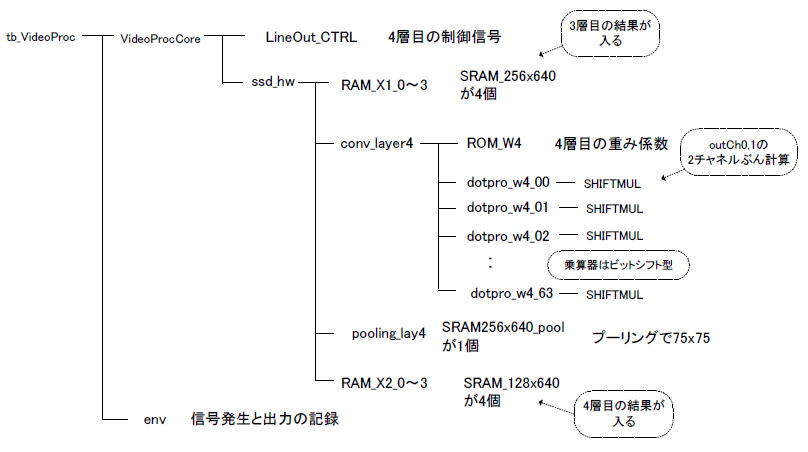

丂vgg-4憌栚偺ModelSim乮僔儈儏儗乕僞乯僾儘僕僃僋僩偺傾乕僇僀僽傪夝搥偡傞偲恾8乚56偺傛偆側峔惉偵側偭偰偄傑偡丅弌椡偑128僠儍僱儖偱偡偑1屄偺愊榓墘嶼婍偱俀僠儍僱儖傪庴偗帩偮偺偱dotpro_W4_xx偼64屄偵側傝傑偡丅傑偨忔嶼婍偼價僢僩僔僼僩宆偱偡丅

丂偙偺憌偼僾乕儕儞僌(pooling_lay4)偑偁傝丄偦傟梡偺儊儌儕(SRAM256x640_pool)偑1屄昁梫偵側傝傑偡丅 |

恾8-56丂vgg-4憌栚偺僣儕乕峔憿

仠儔僀儞偺廃婜偼攞偵側傞偑儔僀儞悢偑敿暘偵側傞

丂3憌栚偺弌椡偼偙偙偵帵偡傛偆偵23.04us x 150 = 3.456ms偱1儔僀儞傇傫偺墘嶼偑廔傢傝傑偡丅恾8乚57傪尒傞偲Lay2NextWrSel乮4憌栚偺擖椡儔僀儞僶僢僼傽偺愗傝懼偊怣崋乯偑3.456ms偱愗傝懼傢偭偰偄傑偡丅

丂4憌栚偺弌椡偵偼僾乕儕儞僌偑偁傞偺偱丄46.08us x 75 = 3.456ms偱1儔僀儞寁嶼偟傑偡偑丄偙偙偺塃壓偺傛偆偵柍岠儔僀儞偺婜娫偑擖傞偺偱丄偦偺攞偺6.912ms偱1儔僀儞弌椡偝傟傑偡丅恾8乚57傪尒傞偲ReluWrSel乮弌椡儔僀儞僶僢僼傽偺愗傝懼偊怣崋乯偑6.912ms偱愗傝懼傢偭偰偄傑偡丅

丂僾乕儕儞僌偵傛傝75儔僀儞偵側傞偺偱1夋柺偺張棟偼6.912ms x 75 = 518.4ms偲側傝丄寢嬊侾丆俀丆俁憌偲摨偠偵側傝傑偡丅 |

恾8-57丂擖椡1儔僀儞偺廃婜偲弌椡1儔僀儞偺廃婜

仠relu.out偵弌椡偑彂偐傟偰偄傞

丂4憌栚傕弌椡偼僥僉僗僩僼傽僀儖偵棊偲偝傟傑偡丅relu.out傪尒傞偲僨乕僞暆偼5

x 128 = 640bit偵側偭偰偄傑偡丅傑偨僾乕儕儞僌偱75亊75夋慺偵側偭偰偄傞偺偱丄1夋柺偱5625峴偵側傝傑偡丅慜憌傑偱偲摨條偵EXCEL偺VBA偱僨乕僞傪暲傃懼偊丄Python偺寢壥偲斾妑偟傑偡丅 |

恾8-58丂75x75 = 5625峴丄奺峴僨乕僞暆偼640價僢僩

仠僶僢僠僼傽僀儖偱傑偲傔偰斾妑偡傞

丂CSV僼傽僀儖偑128屄傕偁傞偺偱丄慜憌傑偱偲摨條偵僶僢僠僼傽僀儖偵傛偭偰斾妑偟傑偡丅偦偺寢壥偼恾8-59偺傛偆偵側傝丄慡偰偺僠儍僱儖偑僺僞儕堦抳偟偰偄傑偡丅 |

恾8-59丂僐儅儞僪僾儘儞僾僩偱test4.bat傪憱傜偣傞

嵟弶偺儁乕僕傊

栚師傊栠傞 |