8-06丂vgg-11, 12, 13憌栚偺VHDL壔

仠11憌栚偼弌椡512ch偱32暲楍

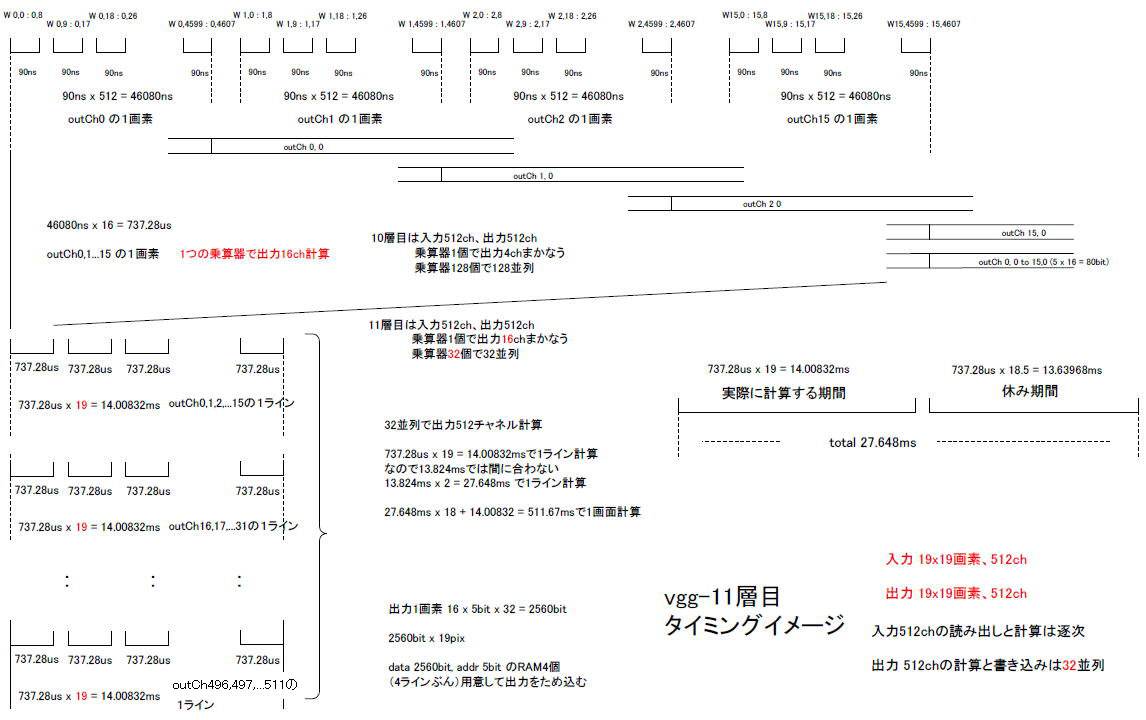

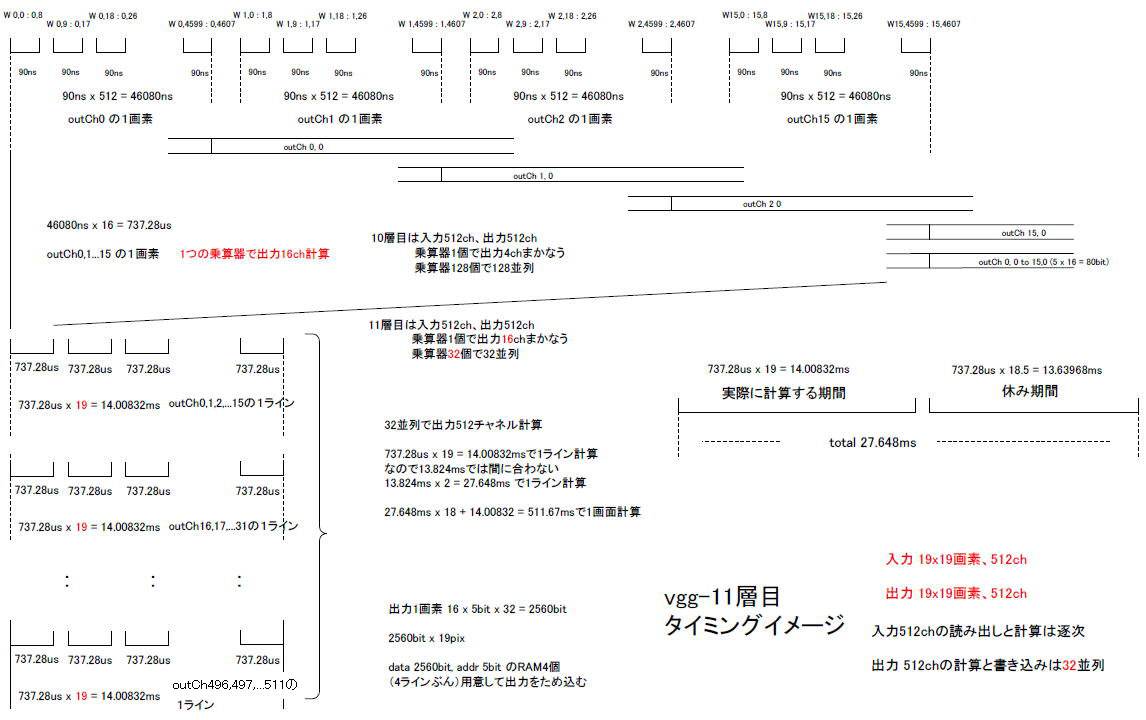

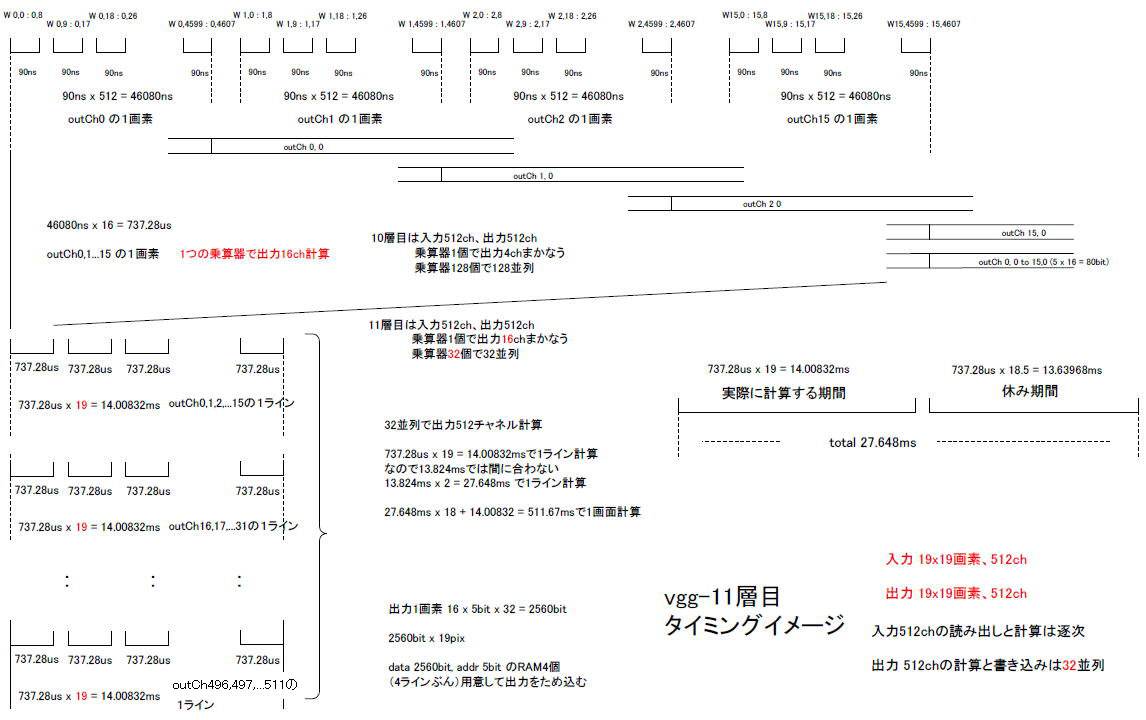

丂恾8乚101偵vgg-11憌栚偺僞僀儈儞僌偺僀儊乕僕傪帵偟傑偡丅

丂11憌栚偺擖椡偼512ch丄弌椡傕512ch偱偡丅擖椡偼拃師張棟丄弌椡偼32暲楍偱寁嶼偟傑偡丅

丂偡側傢偪1偮偺忔嶼婍偱弌椡傪16ch寁嶼偡傞偙偲偵側傝丄偦偆偡傟偽摨恾偺嵍偵偁傞傛偆偵outCh0,1,2,...15偺1儔僀儞偑14.00832ms偱寁嶼偱偒傑偡丅 |

恾8-101丂vgg-11憌栚偺僞僀儈儞僌偺僀儊乕僕

仠8ch亊64暲楍側偺偱弌椡512ch

丂恾8乚101偺忋抜偼outCh0,1,2,...15傪寁嶼偡傞傛偆偡偱偡丅偙傟傜弌椡16ch偼1屄偺忔嶼婍偱乽拃師揑偵乿寁嶼偝傟傑偡丅偟偨偑偭偰1夋慺偺寁嶼偵偐偐傞婜娫偼90ns

x 512 x 16 = 737.28us偵側傝傑偡丅

丂1儔僀儞19夋慺側偺偱737.28 x 19 = 14.00832ms偱1儔僀儞寁嶼偟傑偡偑丄摨恾塃偵偁傞傛偆偵乽媥傒婜娫乿偑13.63968ms偁傞偺偱寁27.648ms偱1儔僀儞丄1夋柺19儔僀儞側偺偱27.648ms

x 19 = 525.312ms偱1夋柺偺寁嶼偑廔傢傝傑偡丅乮仏侾乯

丂乽outCh16 to outCh31乿丄乽outCh32 to outCh47乿丄...乽outCh496 to outCh511乿傕偦傟偧傟1偮偺忔嶼婍偱寁嶼偝傟傑偡丅忔嶼婍乮價僢僩僔僼僩宆乯偑32屄暲楍偱16ch偯偮寁嶼偡傞偺偱弌椡偼512ch偵側傝傑偡乮擖椡傕512ch乯丅

乮仏侾乯幚嵺偼27.648ms x 18 + 14.00832 = 511.67ms偱1夋柺偺寁嶼偑廔傢傞丅518.4ms傛傝彮偟抁偄 |

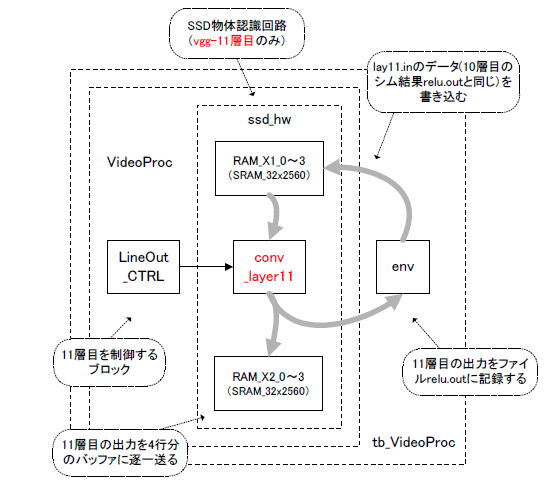

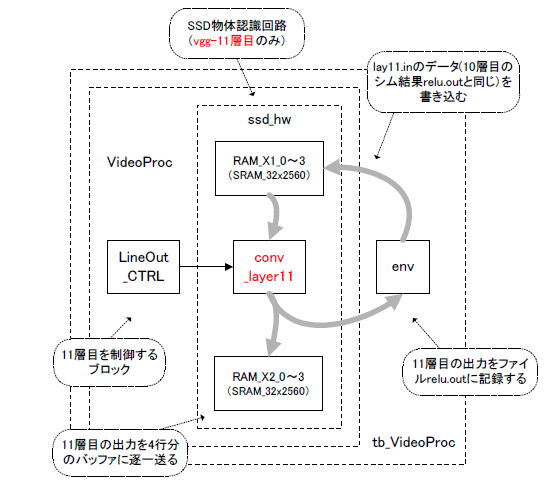

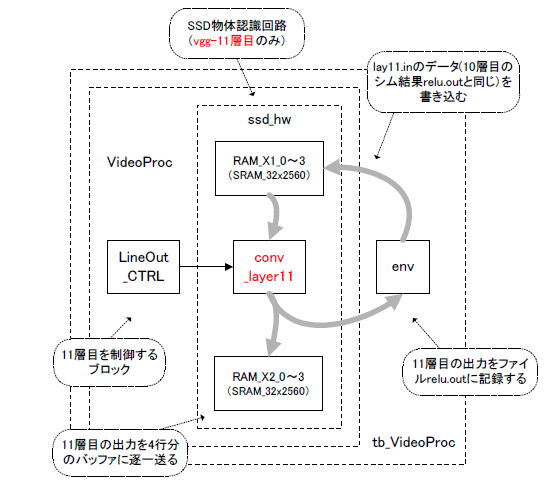

仠10憌栚偺弌椡偑11憌栚偺擖椡偵側傞

丂10憌栚偺僔儈儏儗乕僔儑儞寢壥relu.out偺柤慜傪曄偊偰lay11.in偲偟丄偦傟偑11憌栚偺擖椡偵側傝傑偡丅恾8乚102偺傛偆偵RAM_X1_0乣3乮擖椡僶僢僼傽丄4儔僀儞傇傫乯偵lay11.in偺撪梕偑彂偒崬傑傟傑偡丅

丂conv_layer11偼擖椡僶僢僼傽偐傜偺夋憸傪張棟偟偰RAM_X2_0乣3乮弌椡僶僢僼傽丄4儔僀儞傇傫乯偵彂偒崬傒傑偡丅1儔僀儞19夋慺側偺偱傾僪儗僗偼32丄弌椡512ch側偺偱僨乕僞暆偼5bit

x 512 = 2560bit偵側傝傑偡丅 |

恾8-102丂11憌栚偺僽儘僢僋恾

師偺儁乕僕傊

栚師傊栠傞 |