17-01 認識結果をUARTでホストFPGAに送る

本章ではこのような「複数のFPGAによる認識を統括する仕組み」を考えます。その為にはスレーブFPGAとホストFPGAが通信する必要があります。

スレーブからの情報は、認識された物体の番号、その座標などで情報量はとても少ないため、比較的ゆっくり通信しても間に合います。ここでは通信手段として「UART」を使用します。

ここで作成したQuartusプロジェクトを開き、Platform Designerをクリックします。 |

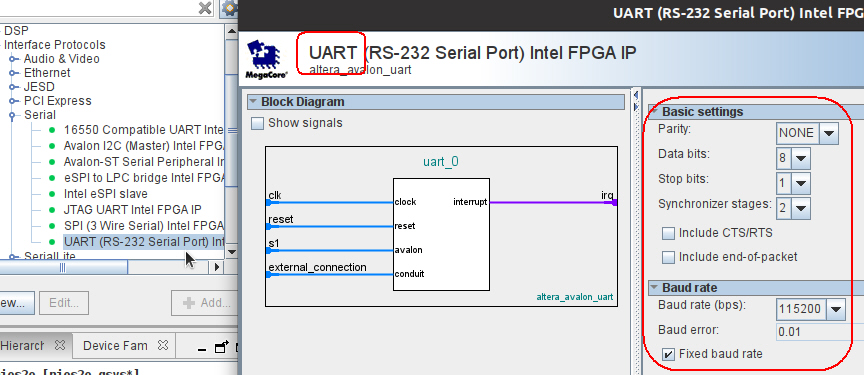

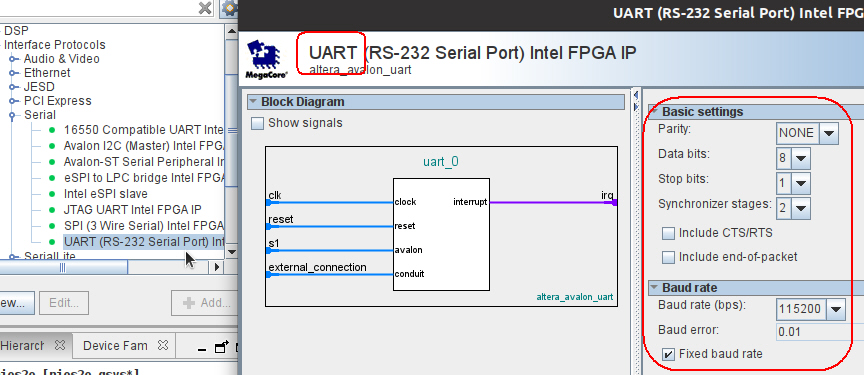

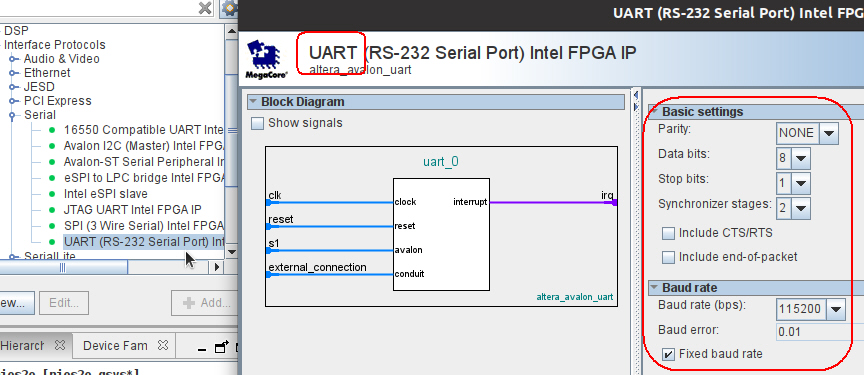

Interface Protocols -> Serial -> UART(RS232...)をダブルクリックし、次のように設定します(Baud Rateは115200bps)。

|

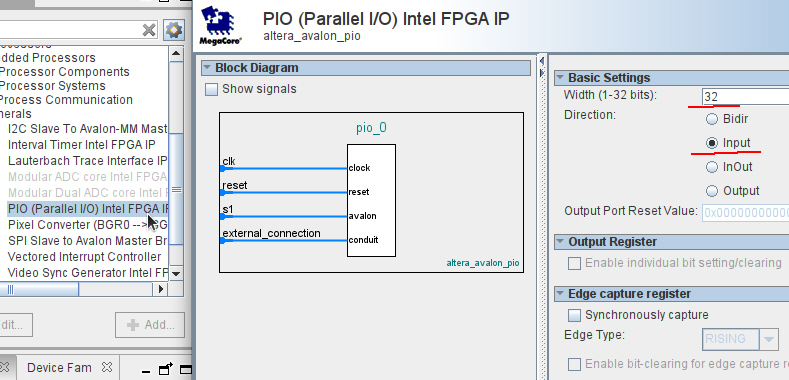

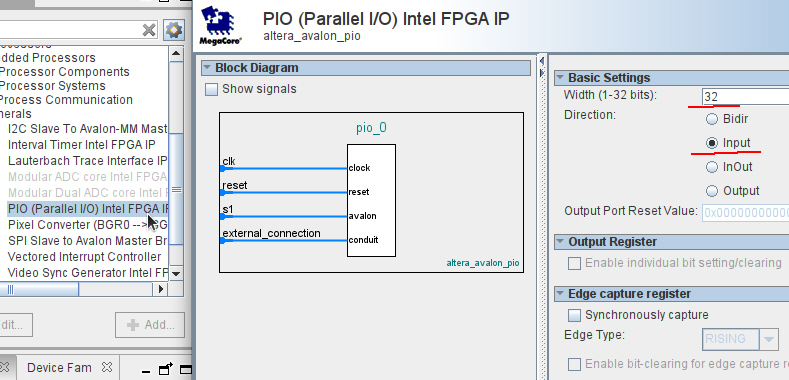

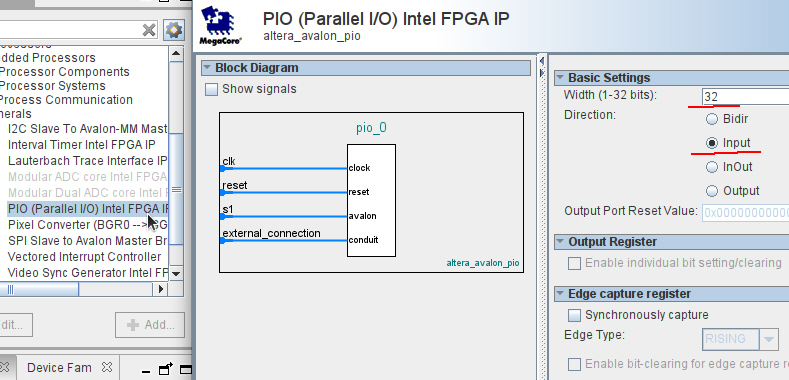

| Processors and Peripherals -> Peripherals -> PIO (Parallel I/O) Intel FPGA IPをダブルクリック。32ビットのInputとします。 |

更にPIOを2つ、計3つ追加します。以下にその一覧。

| 名前 |

in/out |

bits |

| ANSINFO |

Input |

32 |

| ANSADDR |

Output |

9 |

| ANSDATA |

Input |

6 |

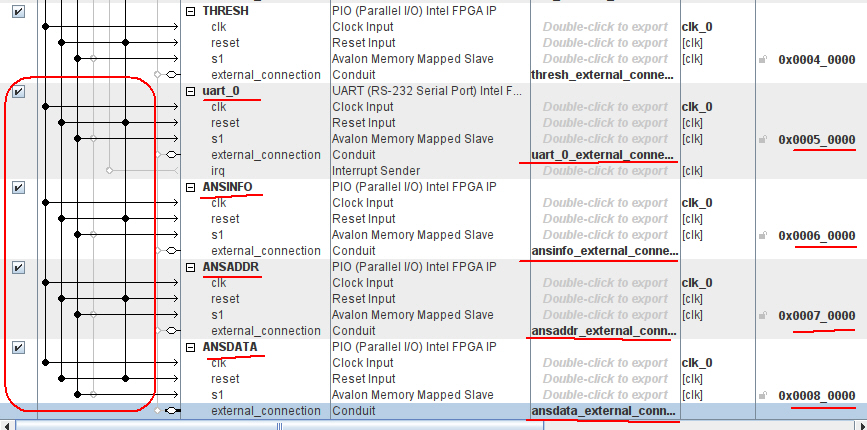

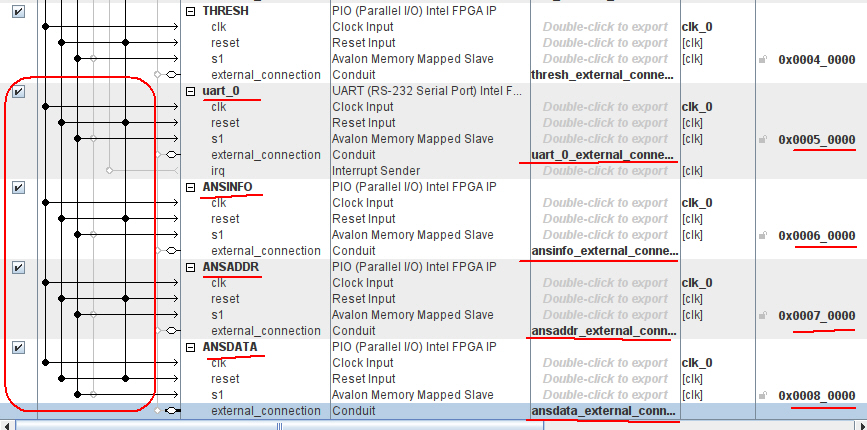

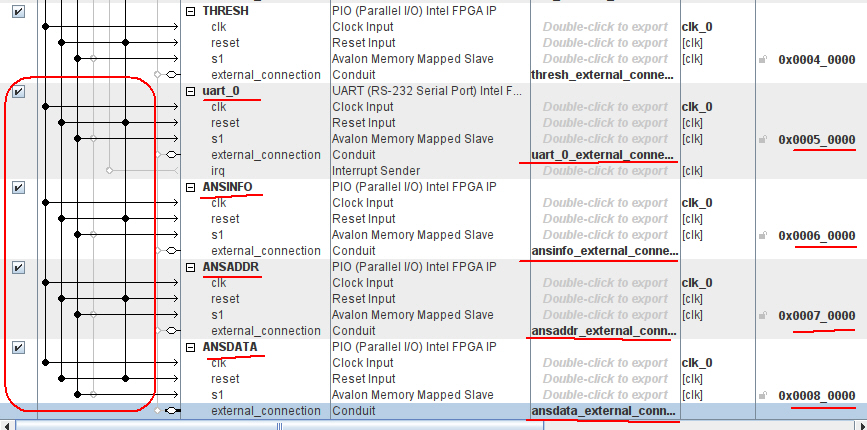

次のように配線、Rename、Exportし、適当にアドレスを振ります。 |

次のページへ

目次へ戻る

|