17-01 認識結果をUARTでホストFPGAに送る(続き)

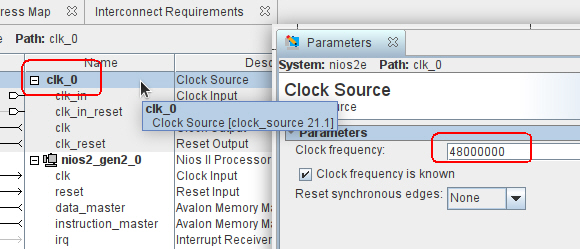

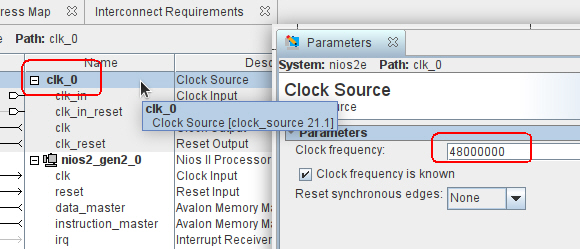

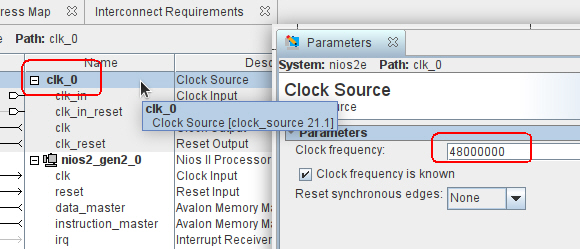

またclk_0をダブルクリックし、Clock Frequencyを48000000にします(*1)。

(*1)Baud Rateを正確に115200HzにするためにPlatform Designerにクロック周波数(48MHz)を伝える。 |

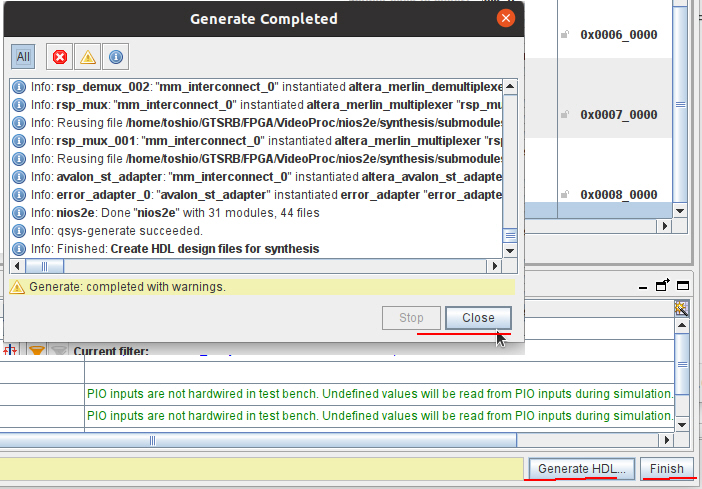

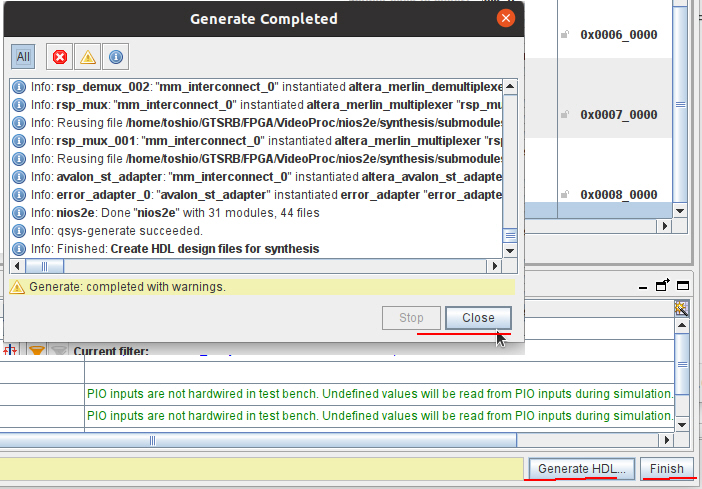

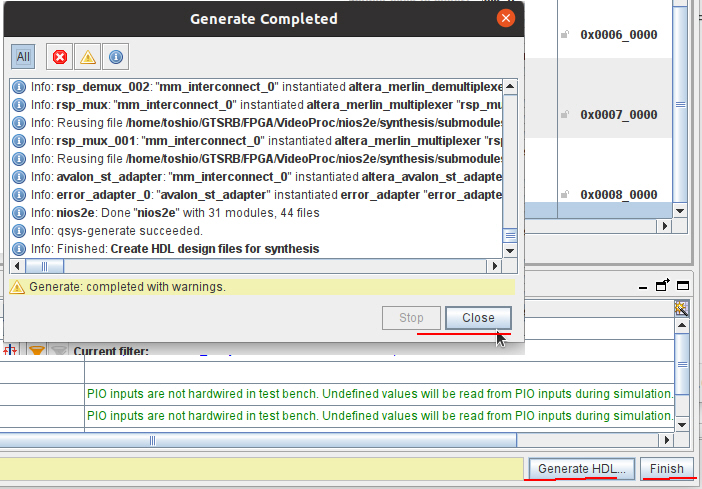

| Generate HDLが成功したらFinishしてPlatform Designerを閉じます。 |

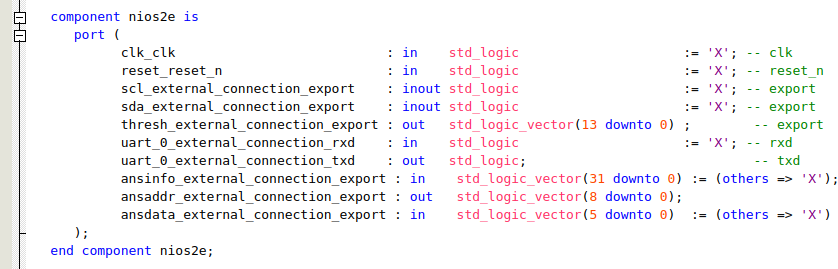

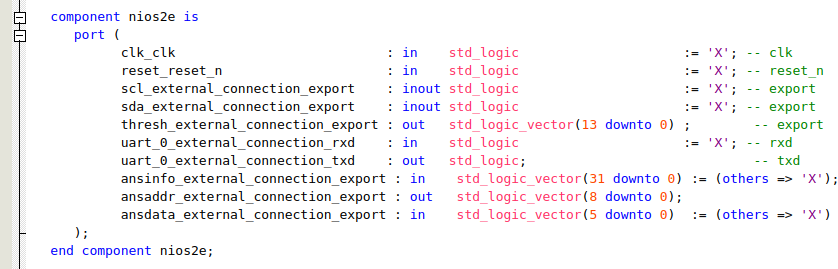

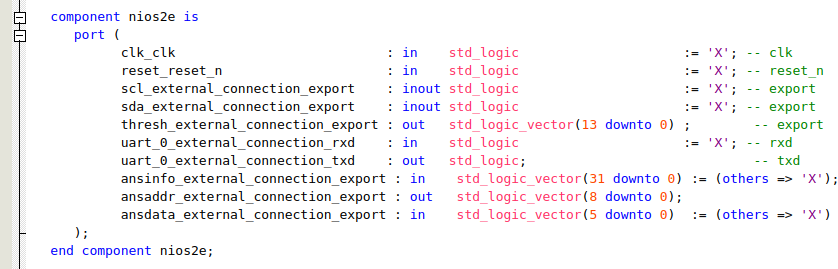

| Quarutus Primeに戻り、component nios2e is...の部分を変更します(これをコピペ)。 |

| 次にnios2eのport mapの部分をこれと置き換えます。 |

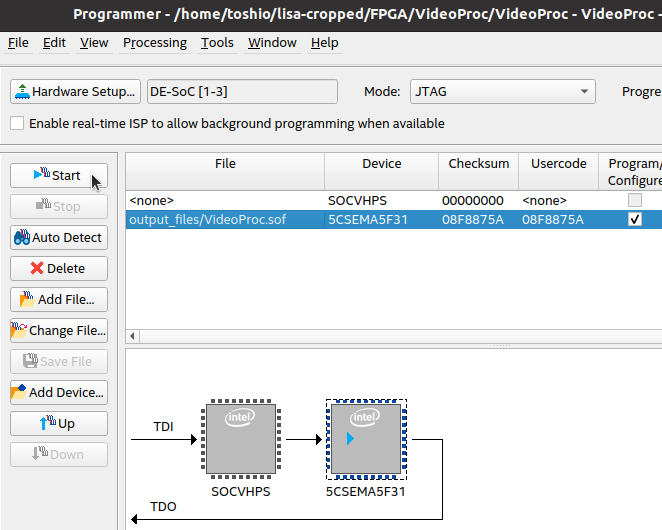

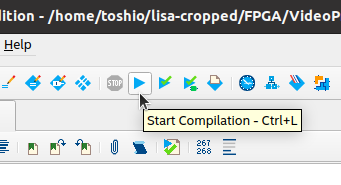

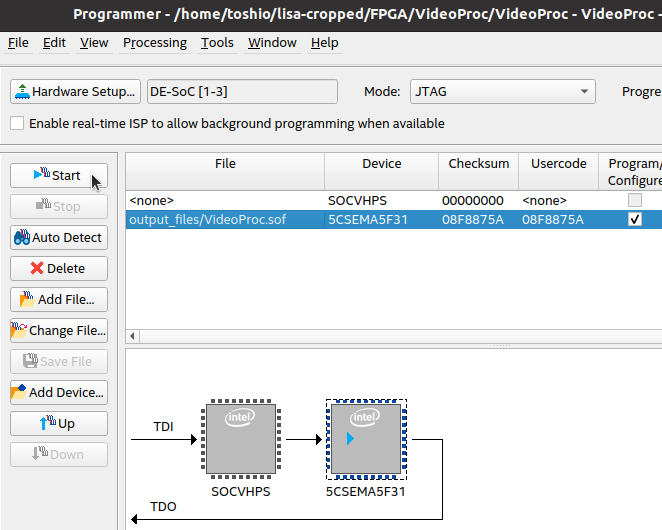

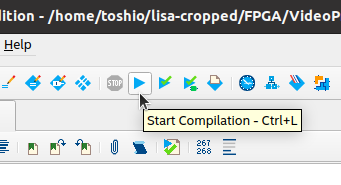

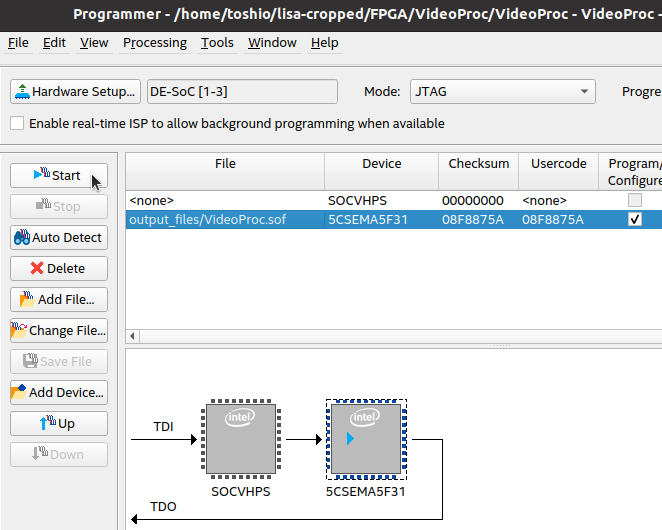

| 論理合成の後はProgrammerで書き込みます。 |

| UARTはNiosIIマイコンから使用します。次のページでその手順。 |

次のページへ

目次へ戻る

|